java

WS2812驱动程序

广域网

皮卡丘

STM32CubeMX

遥感数据处理

图像分割

redux

reference手册

Mybatis框架

hack

AIR32

KVM

期权PCR

pdb

中国计算机学会

Memtor

opencv绘图

图形库

X11

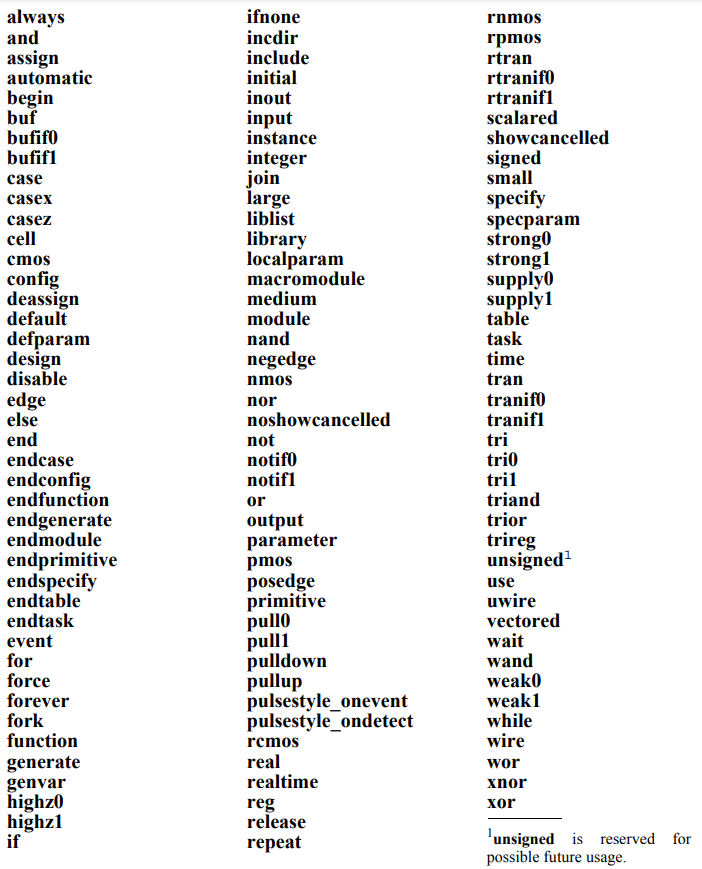

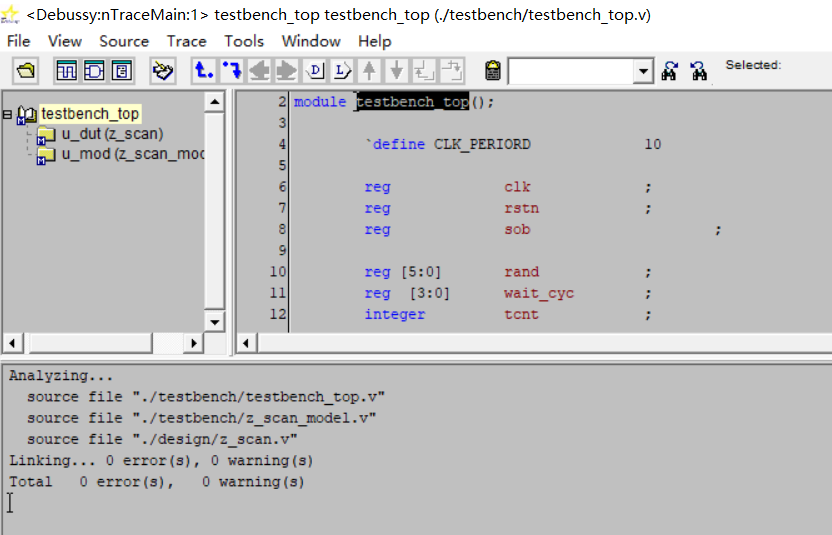

verilog

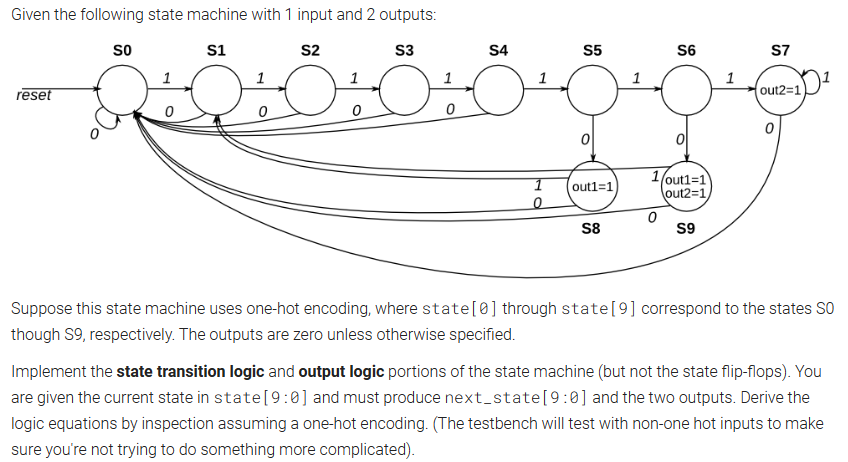

2024/4/11 17:24:27Circuits--Sequential Logic--Finite State Machines--Fsm onehot

网址:https://hdlbits.01xz.net/wiki/Fsm_onehot

module top_module(input in,input [9:0] state,output [9:0] next_state,output out1,output out2);parameter S0 0, S1 1, S2 2, S3 3, S4 4,S5 5, S6 6, S7 7, S8 8, S9 9;assign next_state[S0] (stat…

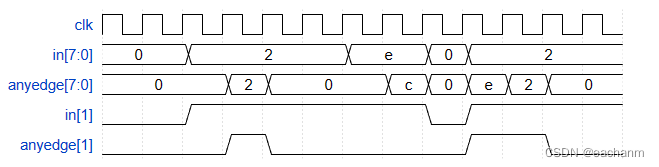

Circuits--Sequential Logic--Latches and Flip-Flops--Edgedetect2

网址:https://hdlbits.01xz.net/wiki/Edgedetect2

module top_module (input clk,input [7:0] in,output [7:0] anyedge

);reg [7:0] r_in;always(posedge clk)beginr_in in;endalways(posedge clk)beginanyedge in ^ r_in;endendmodule

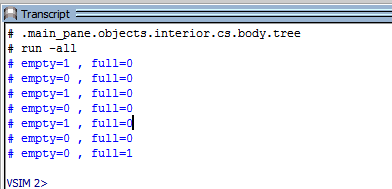

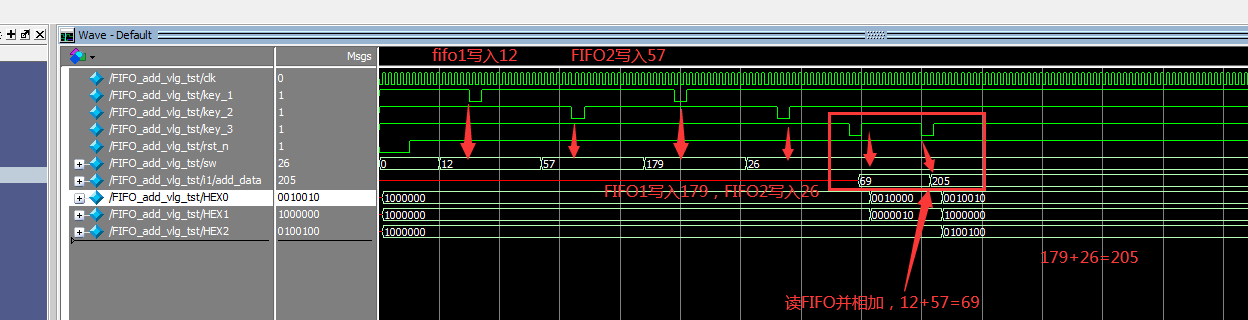

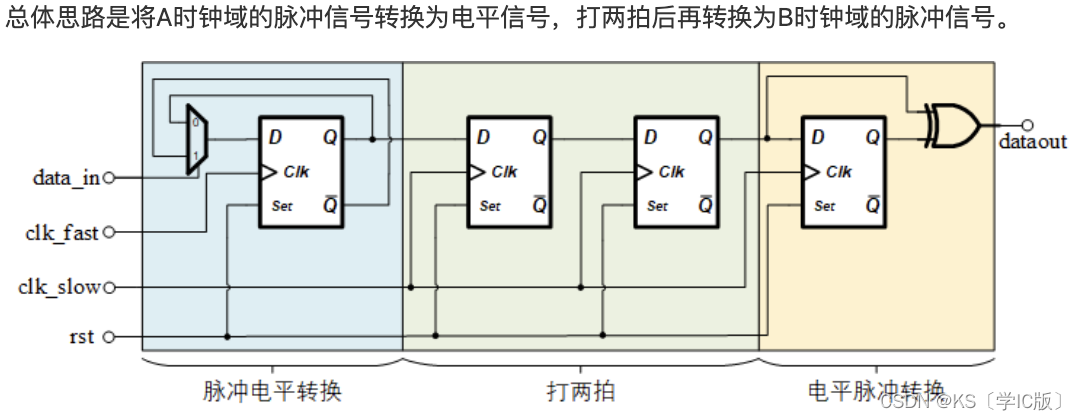

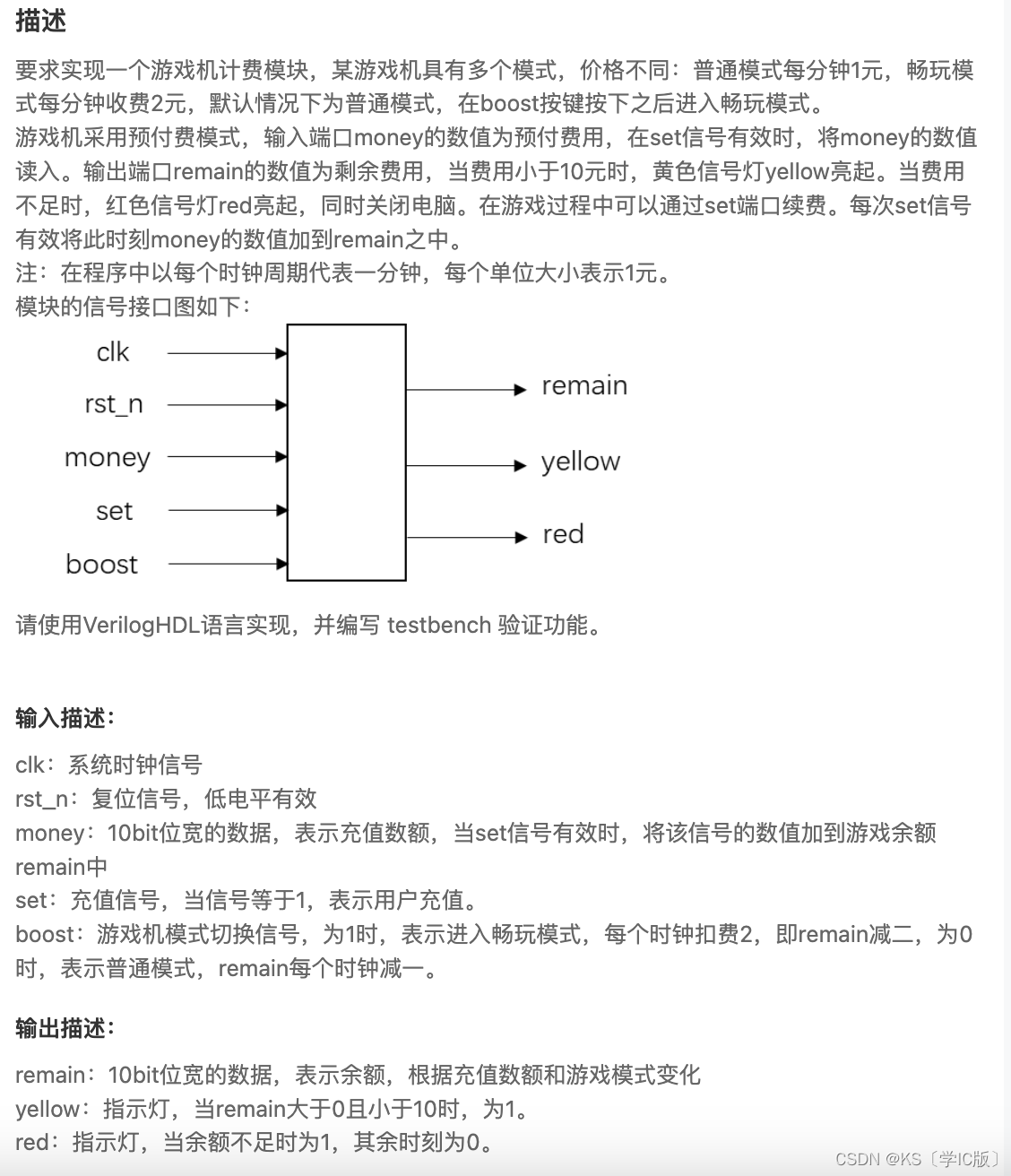

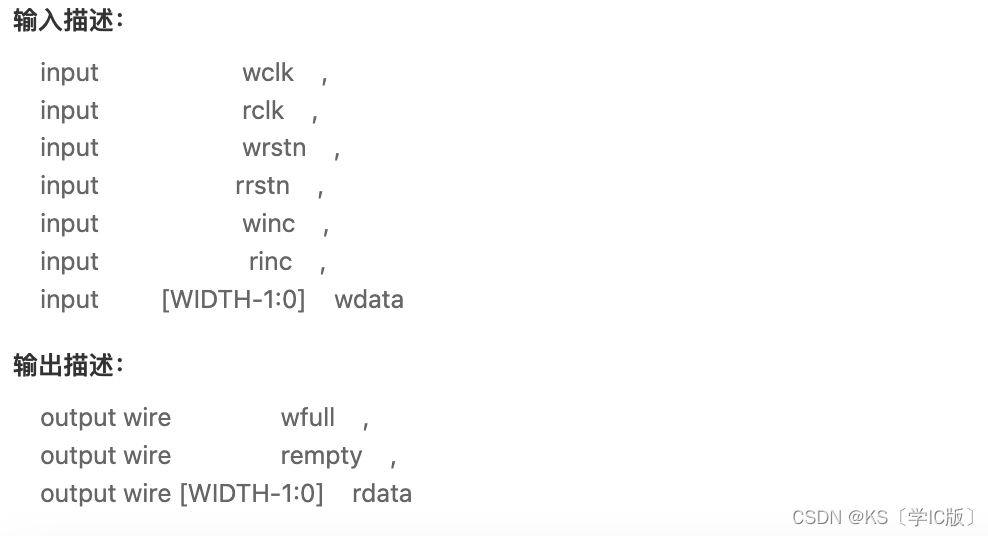

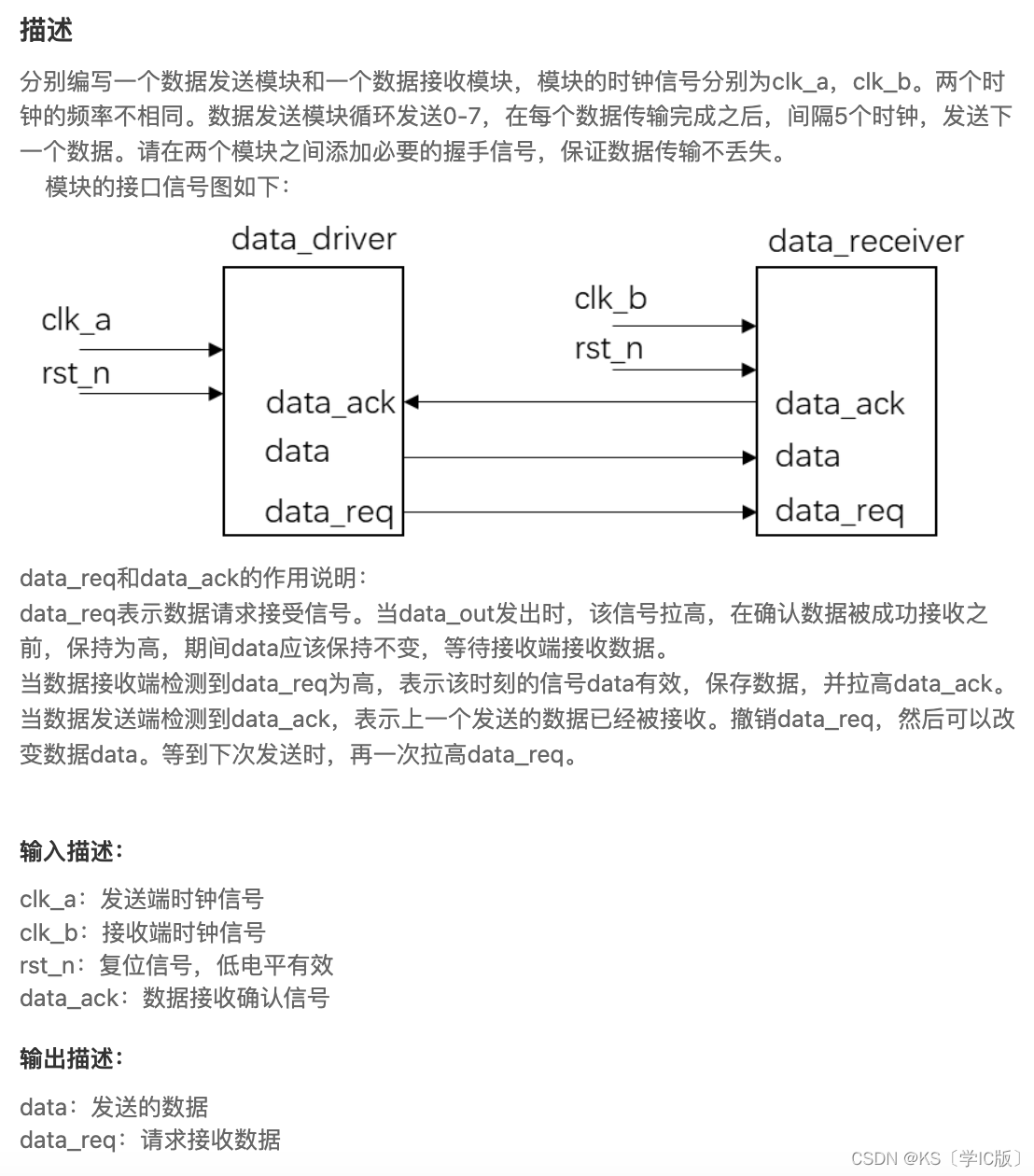

数字芯片设计面试问题——异步FIFO的本质和外延

前言:异步FIFO之所以成为数字芯片设计工程师或者FPGA设计工程师的面试必考问题,在于其设计思想包含了较丰富的跨时钟同步的概念,其中有单比特跨时钟打两拍思想、多比特数据跨时钟和格雷码转换等思想。本文章不仅分析异步FIFO的根本设计原理&a…

Circuits--Combinational Logic--Arithmetic Circuits--Exams/ece241 2014 q1c

网址:https://hdlbits.01xz.net/wiki/Exams/ece241_2014_q1c

module top_module (input [7:0] a,input [7:0] b,output [7:0] s,output overflow

);

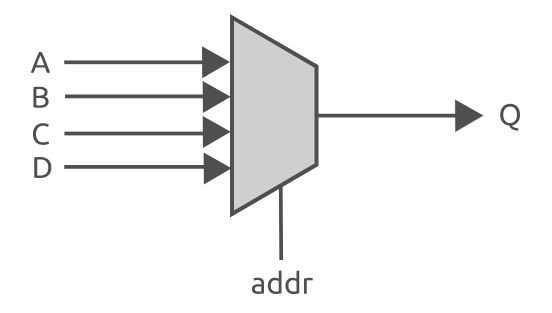

Circuits--Combinational Logic--Multiplexers--Mux256to1v

网址:https://hdlbits.01xz.net/wiki/Mux256to1v

module top_module( input [1023:0] in,input [7:0] sel,output [3:0] out );

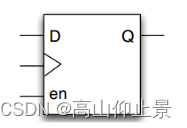

Circuits--Sequential Logic--Latches and Flip-Flops--Exams/2014 q4a

网址:https://hdlbits.01xz.net/wiki/Exams/2014_q4a

module top_module (input clk,input w, R, E, L,output Q

);wire temp1, temp2;assign temp1 E ? w:Q; assign temp2 L ? R:temp1;//与上题类似,不做赘述always (posedge clk)beginQ < tem…

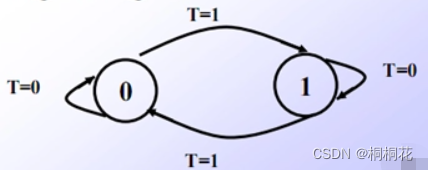

Circuits--Sequential Logic--Finite State Machines--Fsm3onehot

网址:https://hdlbits.01xz.net/wiki/Fsm3onehot

module top_module(input in,input [3:0] state,output [3:0] next_state,output out); //parameter A=0,

Circuits--Sequential Logic--Finite State Machines--Fsm2s

网址:https://hdlbits.01xz.net/wiki/Fsm2s

module top_module(input clk,input reset, // Synchronous reset to OFFinput j,input k,output out); // parameter OFF=1b0;parameter ON =1b1; reg state, next_state;always

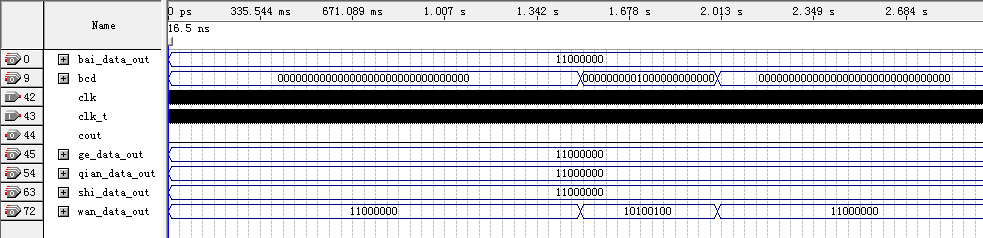

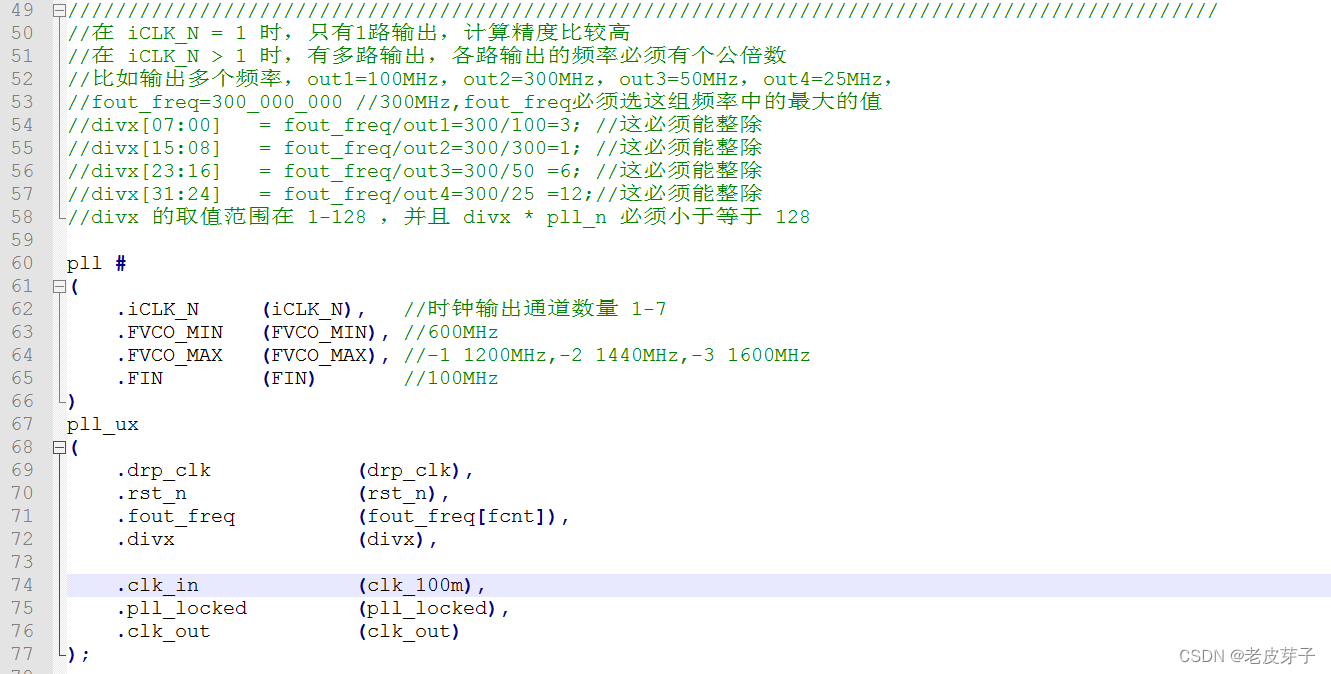

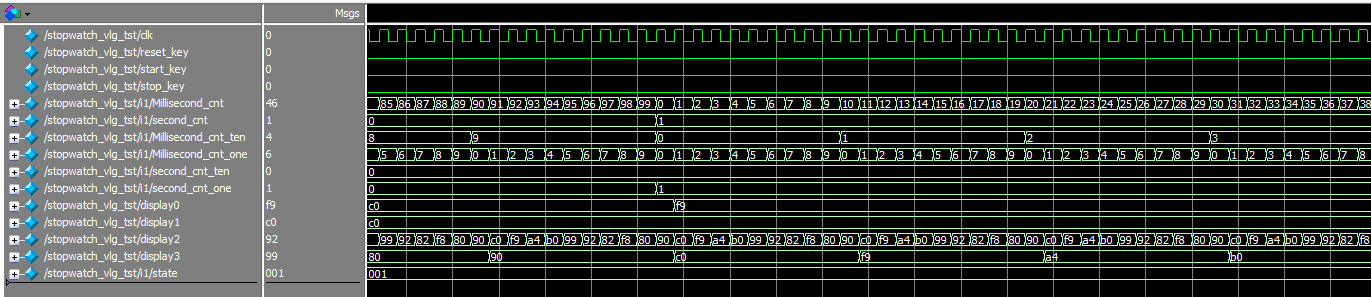

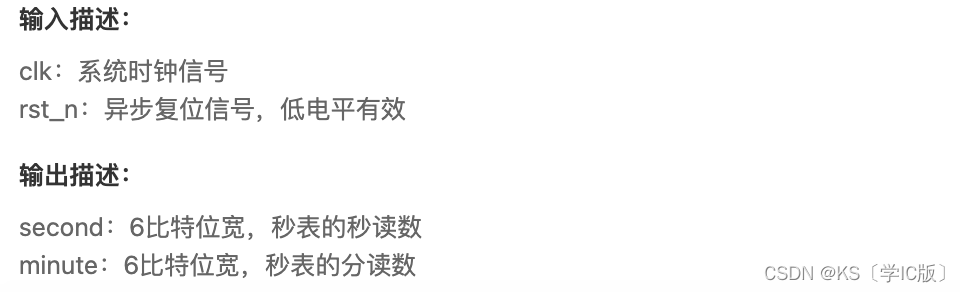

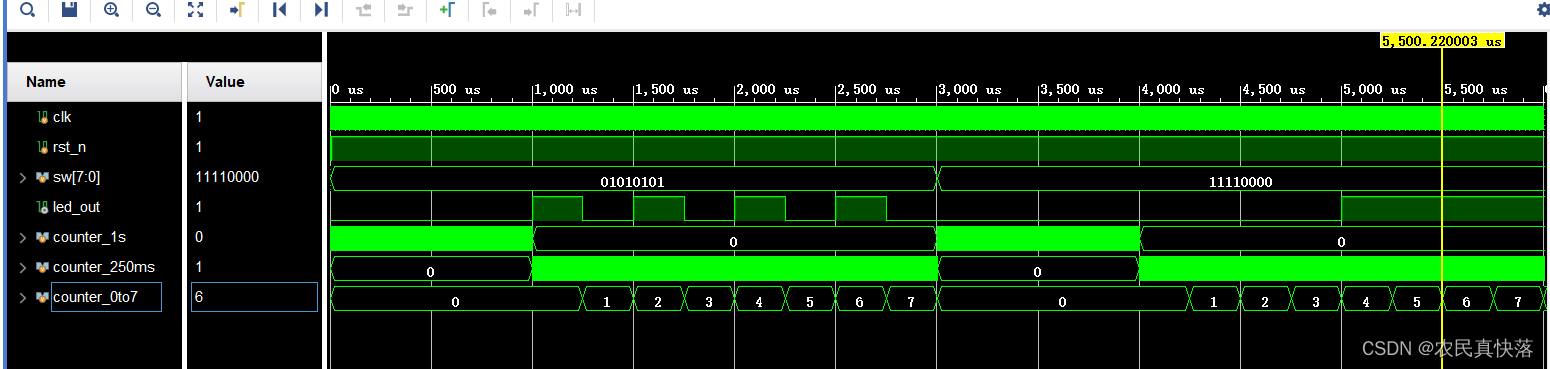

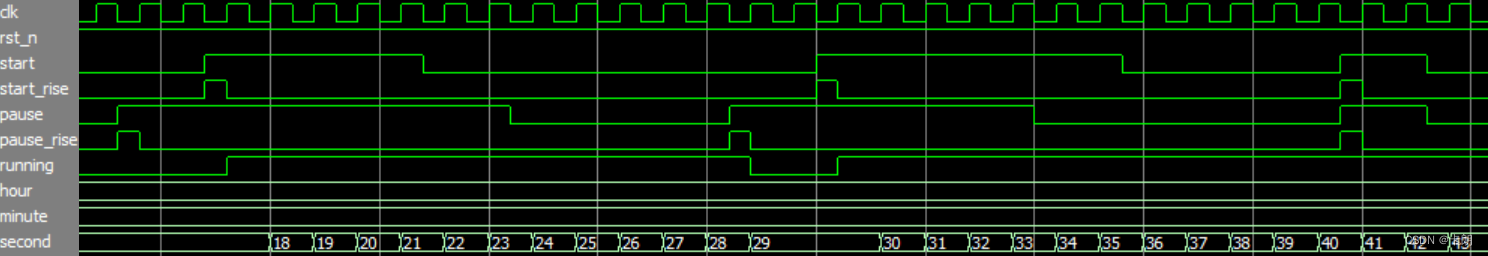

基于FPGA的简易时钟(含verilog源码)

基于FPGA的简易时钟(含verilog源码)

功能分析 1. 具有显示时、分、秒、计时功能,按24小时制计时;(本例实现) 2. 具有校时功能,能够对“时”和“分”进行校时; 3. 具有闹钟功能; 正常计时功能

…

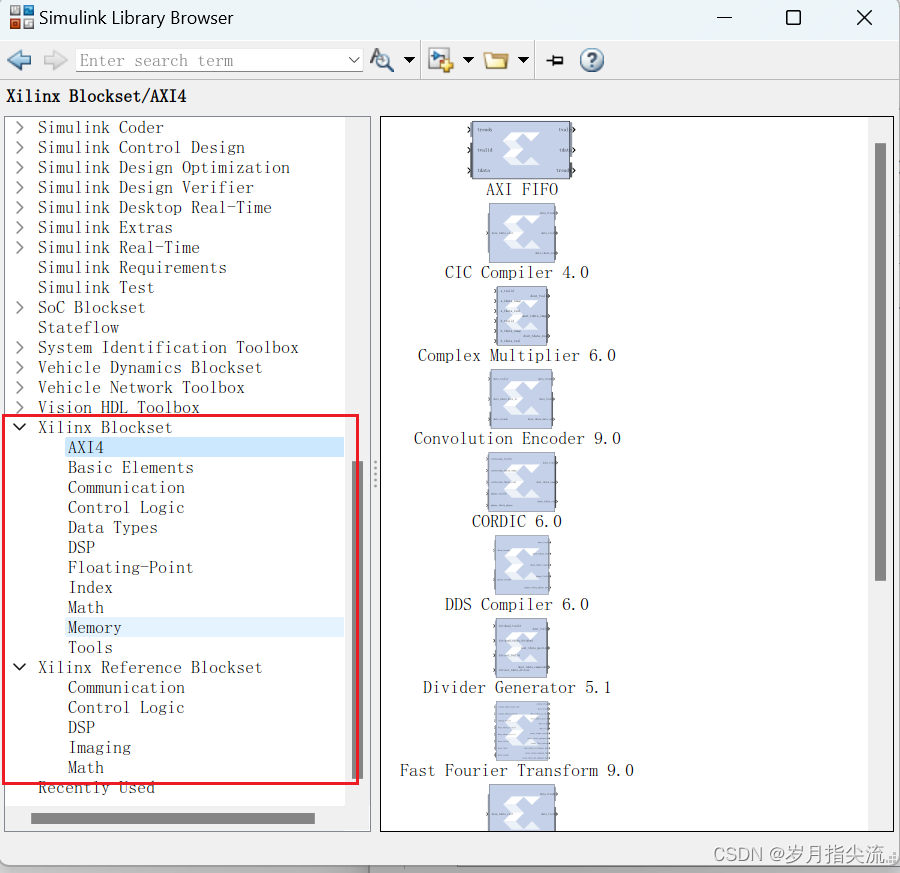

AXI4 协议理解(1)——读写握手

前言:AXI4是ARM公司的一种总线协议,现今无论FPGA还是数字芯片设计,基本都运用AXI或者基于AXI基础上开发IP核。本文通过阅读AMBA AXI™ and ACE™ Protocol specification,提出一些基于自我理解的重点内容,以供大家学习…

Circuits--Sequential Logic--More Cirecuits--Rule90

网址:https://hdlbits.01xz.net/wiki/Rule90

module top_module(input clk,input load,input [511:0] data,output [511:0] q ); always (posedge clk)beginif (load)q < data;elsebeginq < {1b0, q[511:1]} ^ {q[510:0] ,1b0}; endendendmodule

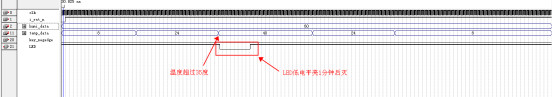

LED按键进阶Verilog

LED进阶

实现闪烁的效果 module LED

(CLK_50M,RST_N,LED1

);input CLK_50M;

input RST_N;

output LED1;reg [26:0] time_cnt;

reg [26:0] time_cnt_n;reg led_reg;

reg led_reg_n;parameter SET_TIME_1S27d50_000_000;always (posedge CLK_50M or negedge RST_N)

begin

…

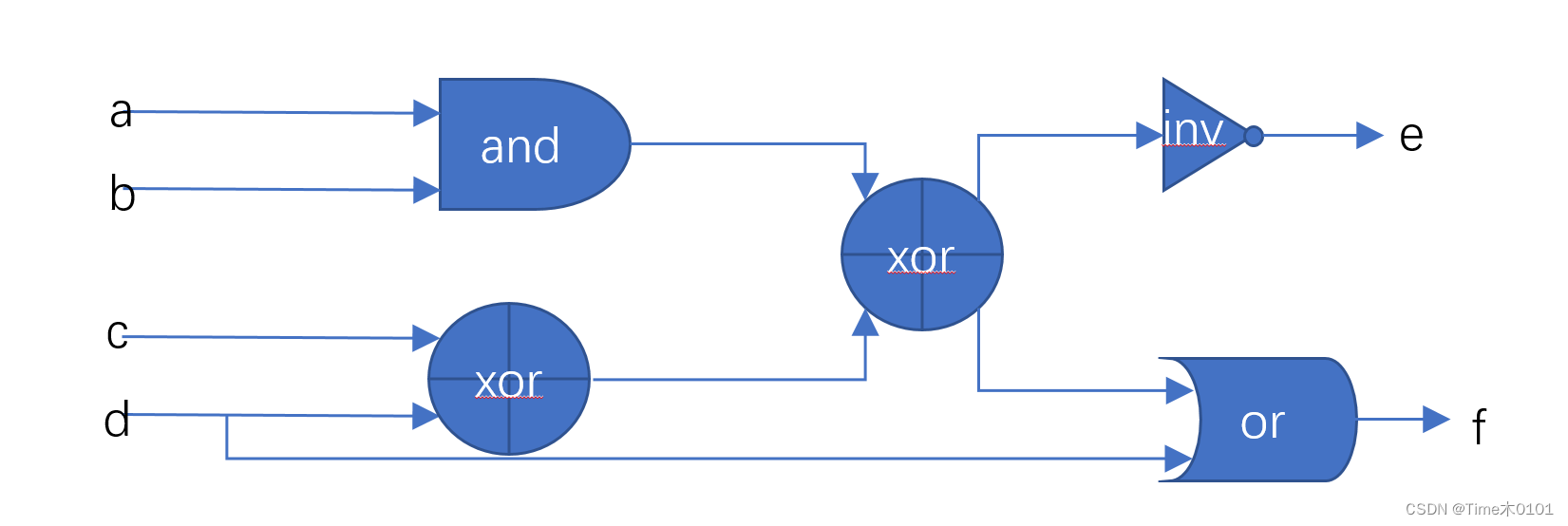

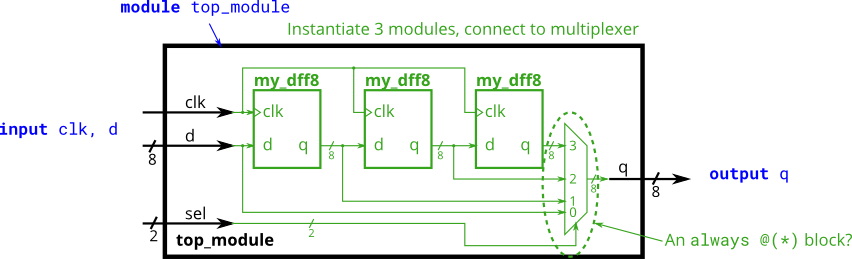

HDLBits学习------Problem 19~27

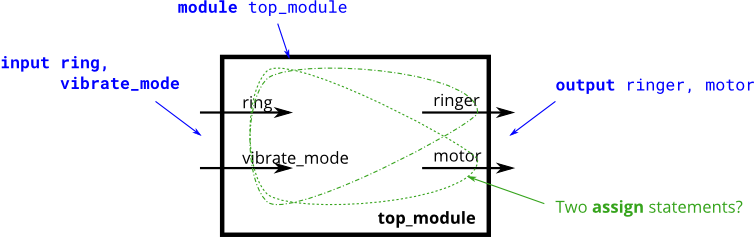

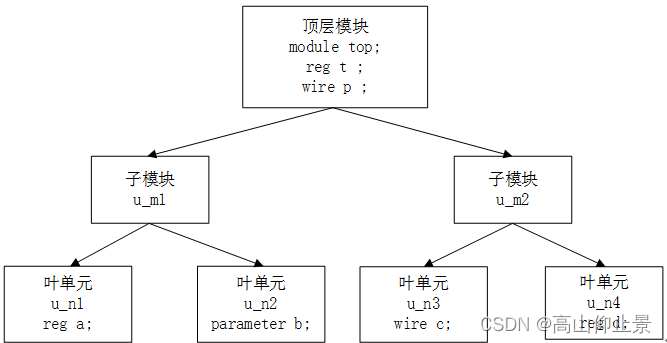

参考链接:HDLBits导学 Problem 19 : Modules 问题:在顶层模块中例化下面的模块 思路:例化有两种方式

按端口顺序,mod_a instance1 ( wa, wb, wc );根据原模块的端口顺序例化(端口列表发生变化后修改很麻烦)…

HDLBits学习------Problem 65~71

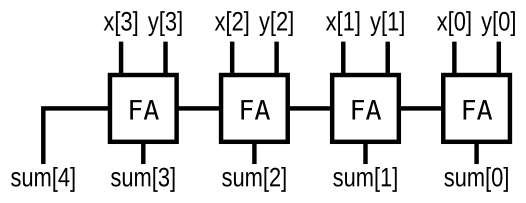

参考链接:HDLBits导学 Problem 65 : Half adder (Hadd) 问题:本题中需要实现一个 2 进制 1bit 加法器,加法器将输入的两个 1bit 数相加,产生两数相加之和以及进位 思路:参考全加器的写法 解决:

module top…

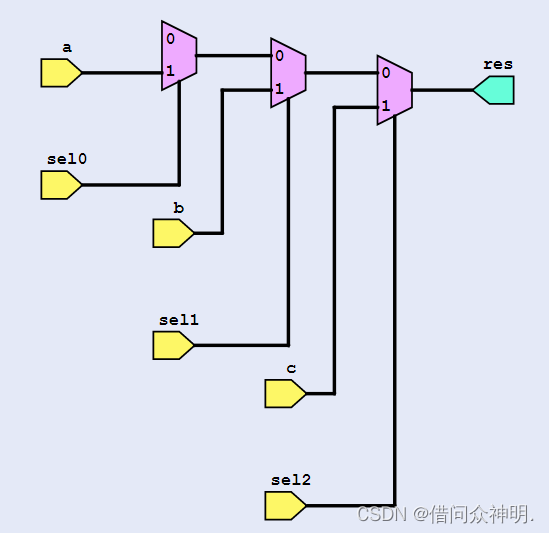

HDLBits学习------Problem 60~64

参考链接:HDLBits导学 Problem 60 : 2-to-1 multiplexer (Mux2to1) 问题:本题中需要实现一个 2 选 1 选择器,sel 信号作为选择信号,当 sel 1 时选择 b,反之选择 a 解决:

module top_module( input a, b, …

HDLBits学习------Problem 131~137

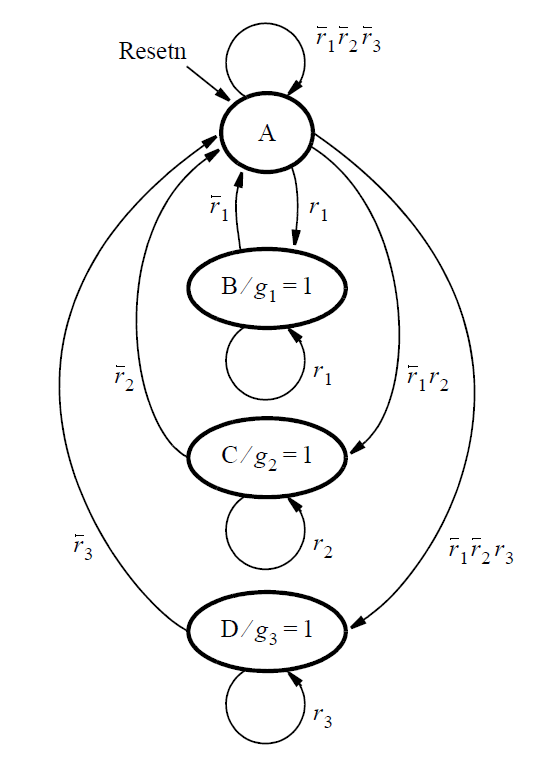

参考链接:HDLBits导学 Problem 131 One-hot FSM / Fsm onehot 问题:下图是具有1个输入和2个输出的状态转移图: 假设该状态机使用独热码,state[0]到state[9]分别对应于状态S0到S9。图中没有标注的输出均为0。 下面请实现状态机的状…

HDLBits学习------Problem 43~59

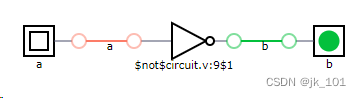

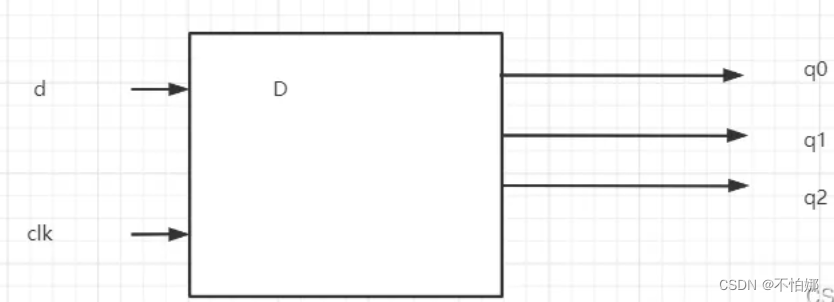

参考链接:HDLBits导学 Problem 43 Wire 问题:实现如下电路 解决:

module top_module (input in,output out);assign out in;endmodule Problem 44 GND 问题:实现如下电路 解决:

module top_module (output out);ass…

HDLBits学习------Problem 118~126

参考链接:HDLBits导学 Problem 118 Simple FSM1 / Fsm1 问题:图中是一个有两个状态的摩尔型状态机。有一个输入信号与一个输出信号。本题中需要实现图中的状态机,注意复位后状态为 B,复位采用异步复位 思路:三段式状态…

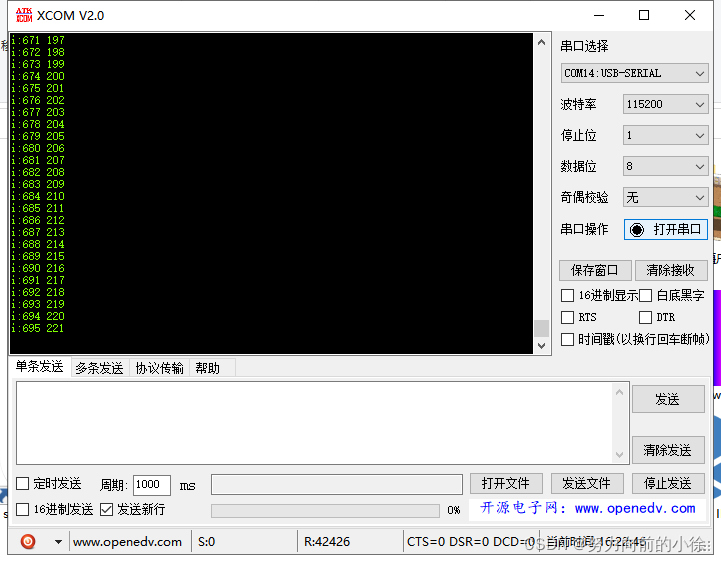

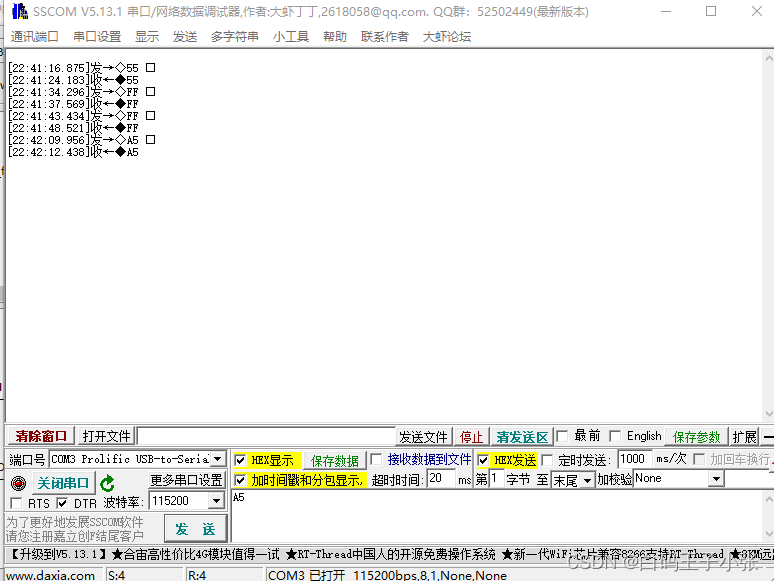

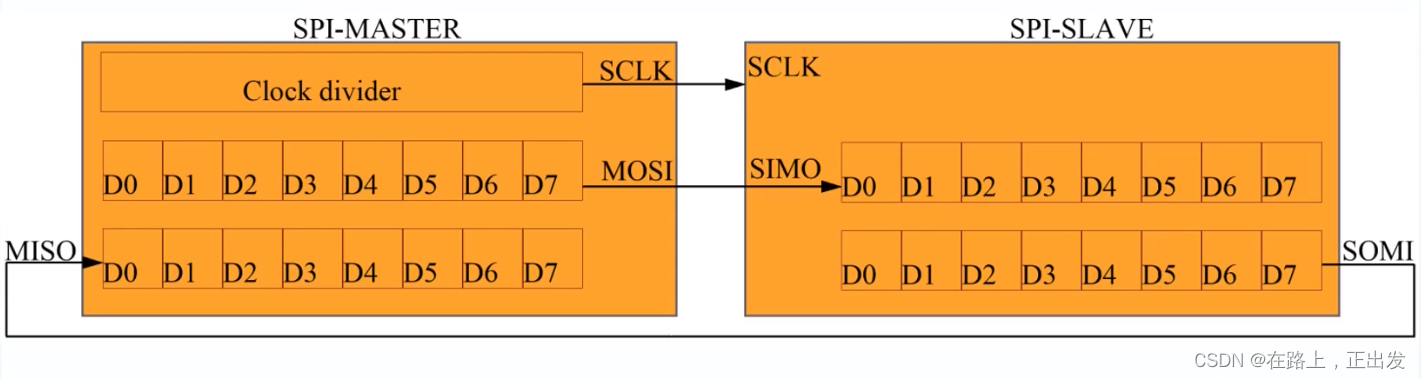

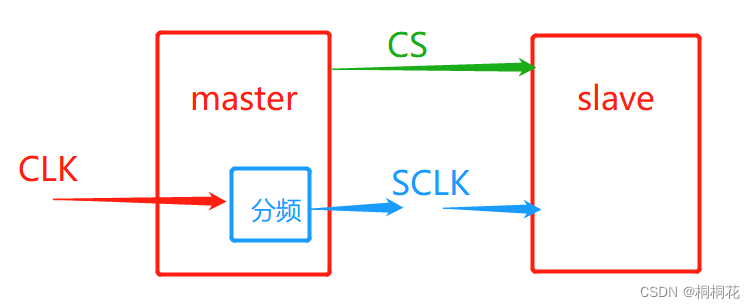

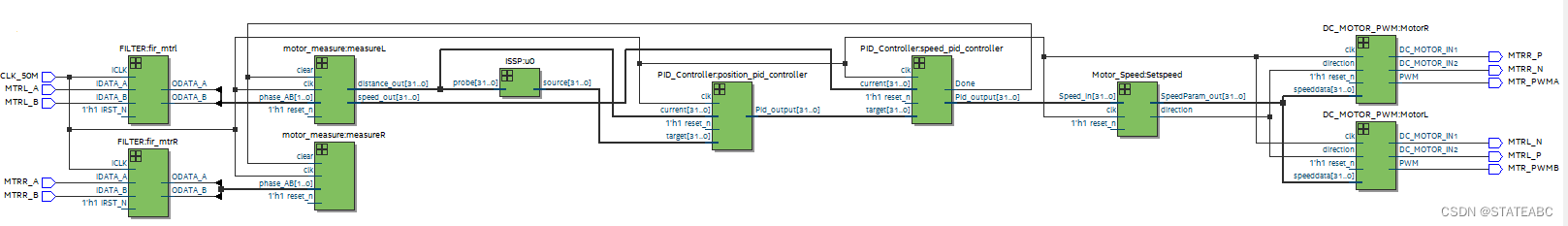

FPGA(主)与STM32(从)SPI通信

一、概述 主要实现了FPGA向STM32快速发送数据(比较稳定),至于STM32发送过来的数据,大概率还是处于丢位状态。但因为我主要是要完成一个FPGA这边持续向STM32的发送,所以我也没仔细去研究如何实现双方通信更稳定…

Circuits--Sequential Logic--Finite State Machines--Fsm3comb

网址:https://hdlbits.01xz.net/wiki/Fsm3comb

module top_module(input in,input [1:0] state,output [1:0] next_state,output out); //parameter A=0,</

Verilog Language--More Verilog Features--Popcount255

网址:https://hdlbits.01xz.net/wiki/Popcount255

module top_module( input [254:0] in,output [7:0] out );reg [254:0] i;always@

Circuits--Sequential Logic--Shift Registers--Lfsr32

网址:https://hdlbits.01xz.net/wiki/Lfsr32

module top_module(input clk,input reset, // Active-high synchronous reset to 32h1output [31:0] q

); reg [31:0] q_next;always @ (

Circuits--Combinational Logic--Basic Gates--Gatesv

网址:https://hdlbits.01xz.net/wiki/Gatesv

module top_module( input [3:0] in,output [2:0] out_both,output [3:1] out_any,output [

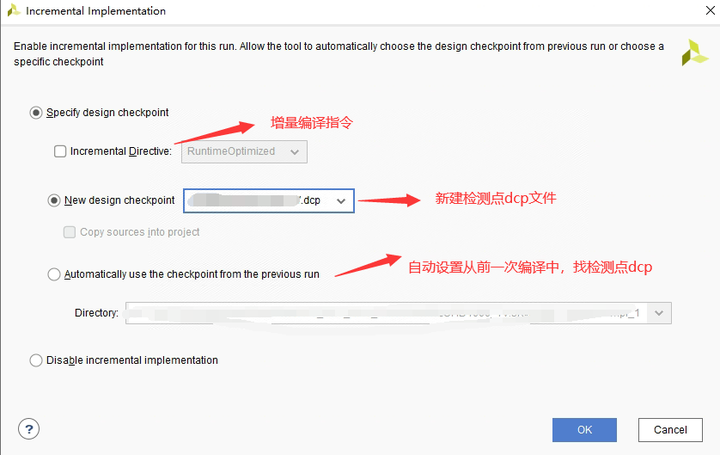

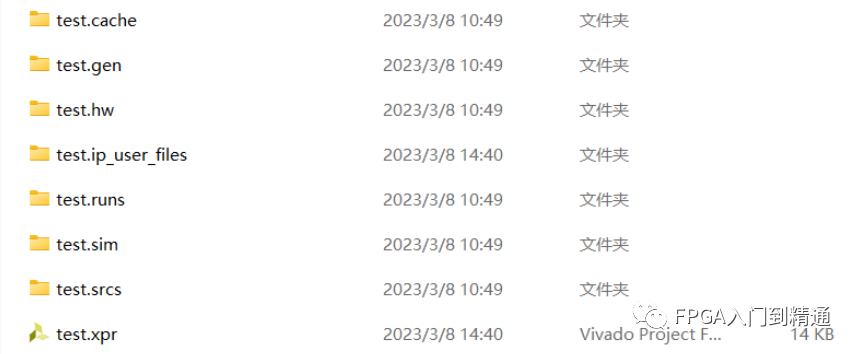

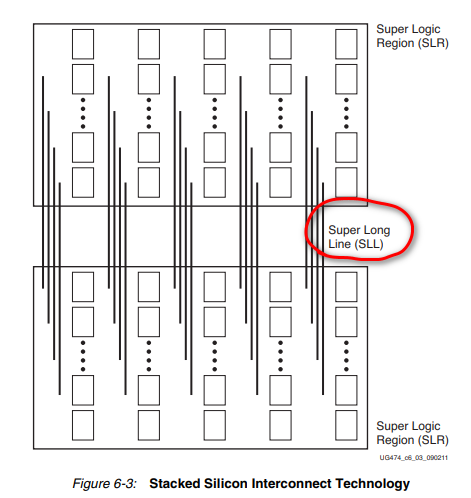

Vivado增量编译:加速FPGA设计实现的利器

随着FPGA设计的复杂度不断提高,设计人员需要选择更为高效的设计流程来保证开发效率和减少开发成本。其中,Vivado增量编译是一种非常重要的设计流程。本文将介绍Vivado增量编译的基本概念、优点、使用方法以及注意事项。

通过阅读本文可以了解࿱…

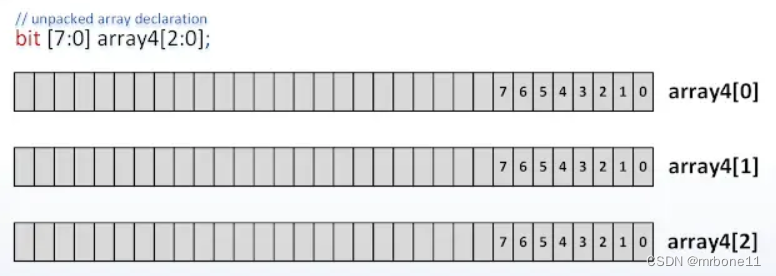

Verilog Language--Vectors--Vector4

网址:https://hdlbits.01xz.net/wiki/Vector4

module top_module (input [7:0] in,output [31:0] out );//assign out {{24{in[7]}},in};endmodule

「Verilog学习笔记」格雷码计数器

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 timescale 1ns/1nsmodule gray_counter(input clk,input rst_n,output reg [3:0] gray_out

);reg [3:0] binary_cnt ; reg flag ; always (posedge clk or negedge r…

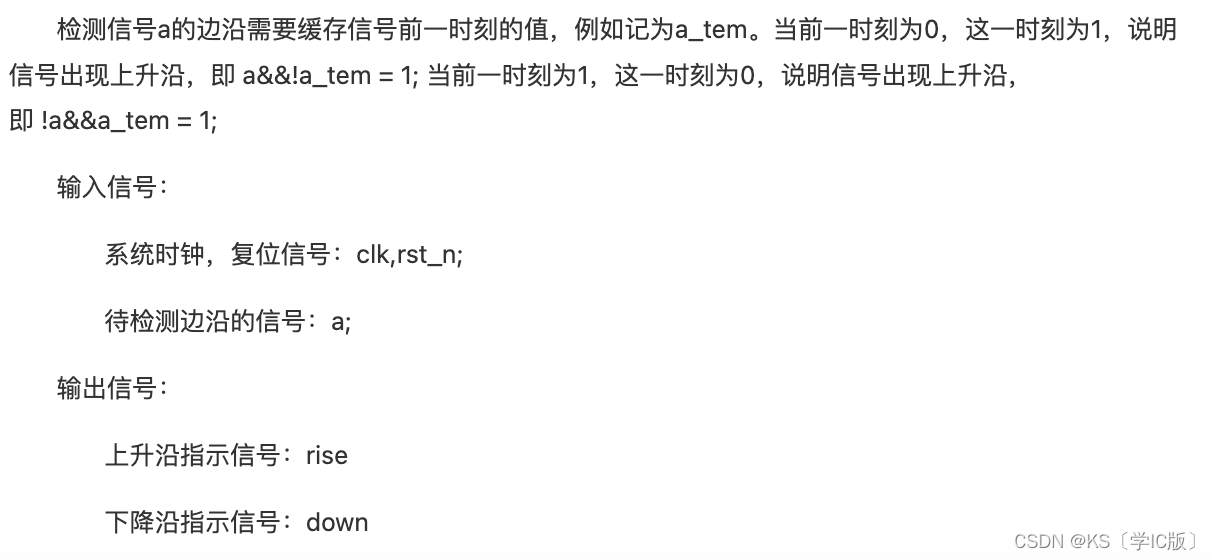

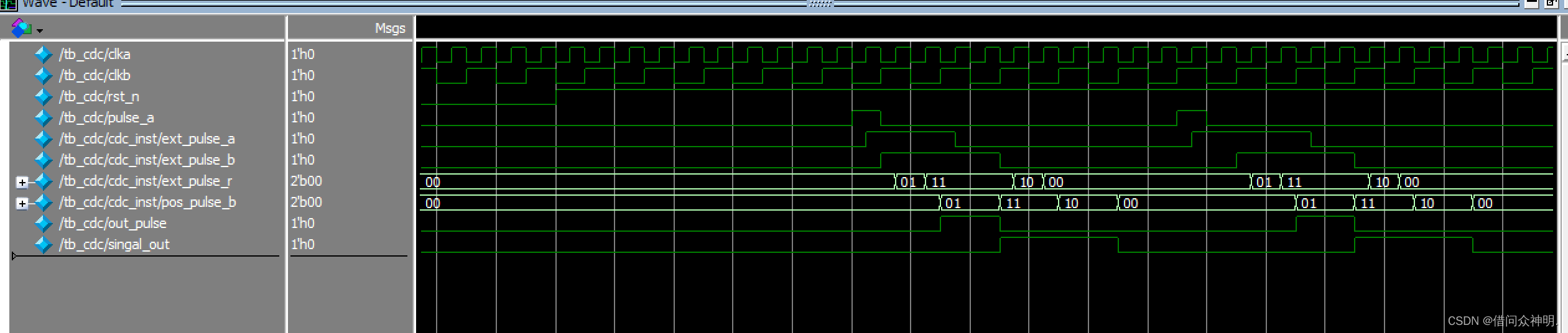

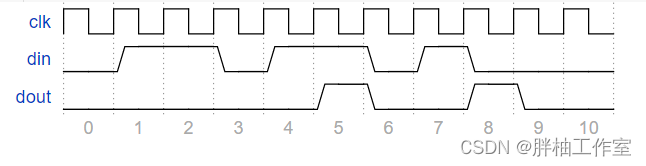

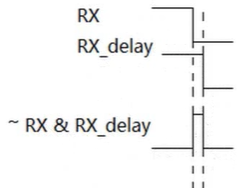

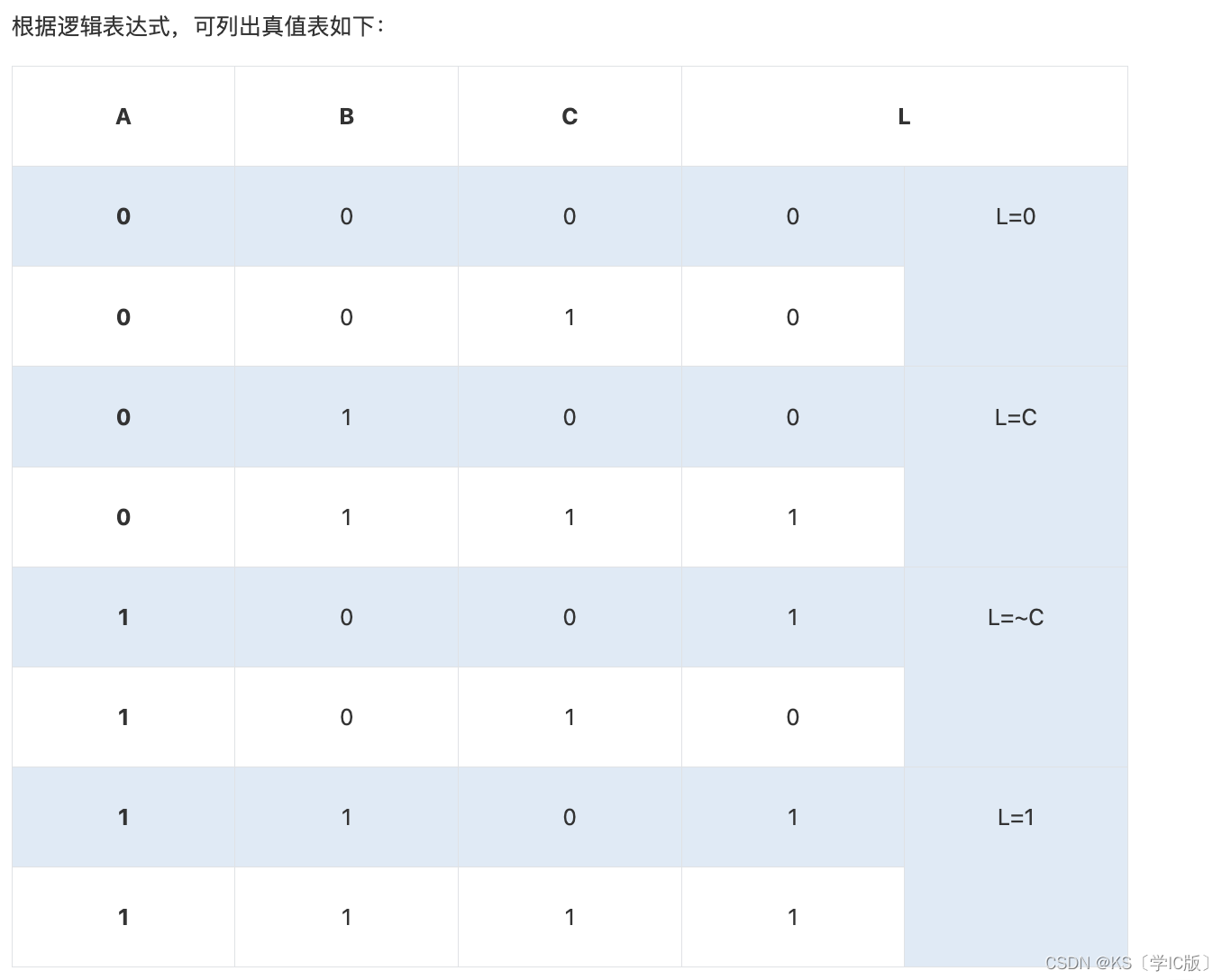

用verilog实现脉冲检测

代码思路和上一篇边沿检测基本一致,通过使用两个触发器,并结合逻辑组合实现检测

但要注意题目里对pulse的定义是什么,本题中pulse是指一个时钟周期宽度的窄脉冲

verilog代码:

module pulse_detector(input clk, rst_n, din, ou…

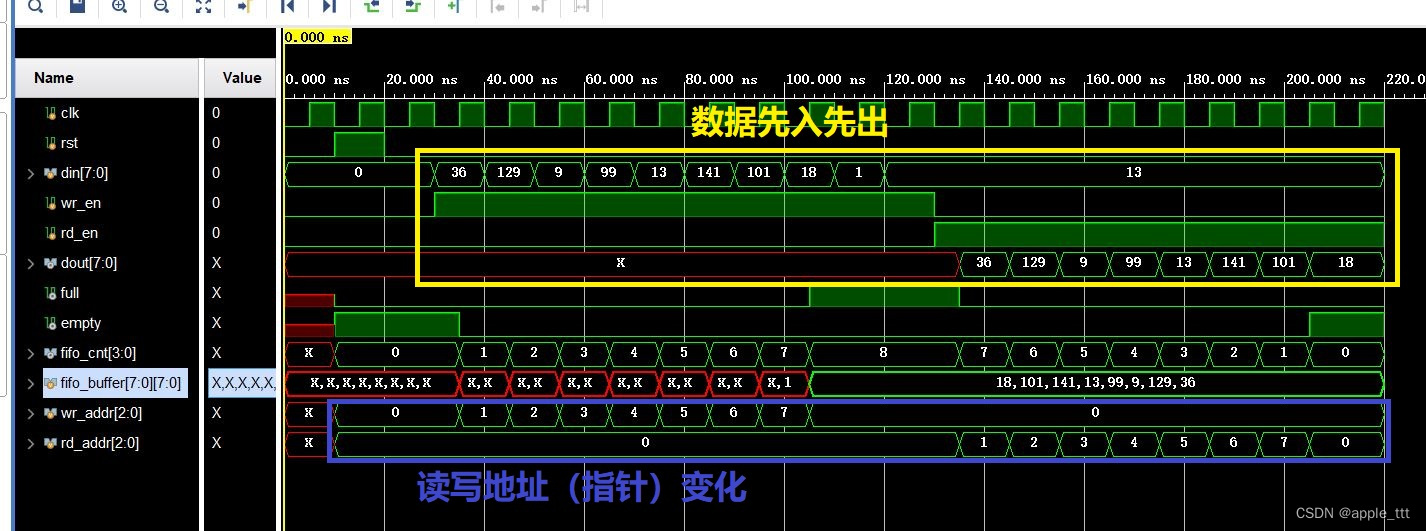

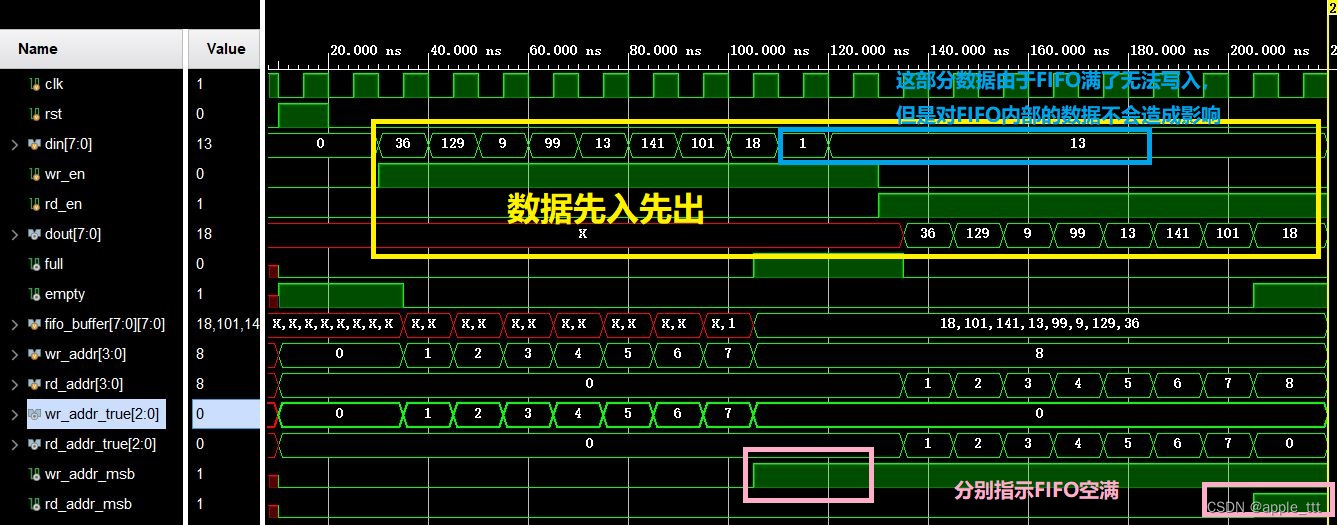

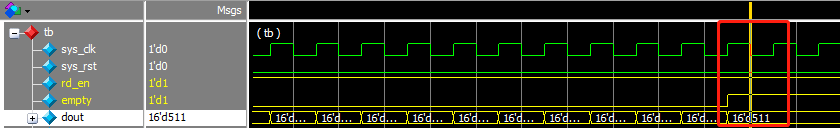

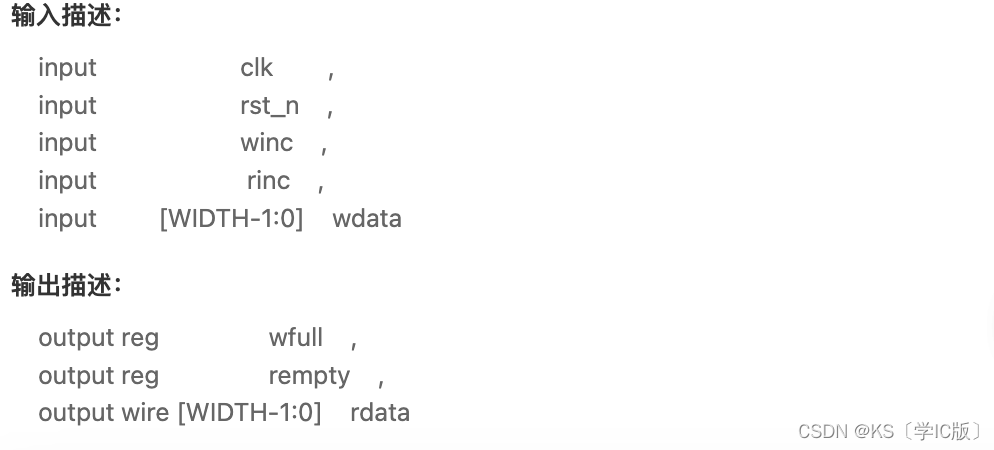

用verilog实现异步fifo

本文实现了异步FIFO

代码思路参考了博客 https://blog.csdn.net/u014070258/article/details/90052281

之后可能会学习一下怎么利用状态机实现FIFO

define FIFO_DEPTH 108//FIFO深度

define FIFO_WIDTH 16//FIFO宽度module asynfifo(

input rst_n,//复位信号

input [FIFO_W…

EDA实验-----4*4矩阵键盘与数码管显示测试

目录

一、实验目的

二、实验仪器设备

三、实验原理

四、实验要求

五、实验步骤

六、实验报告

七、实验过程

1.矩阵键盘按键原理

2.数码管原理

3.分频器代码 4.电路图连接 5.文件烧录 一、实验目的

了解数码管的工作原理;掌握4*4矩阵键盘和数码管显示的编…

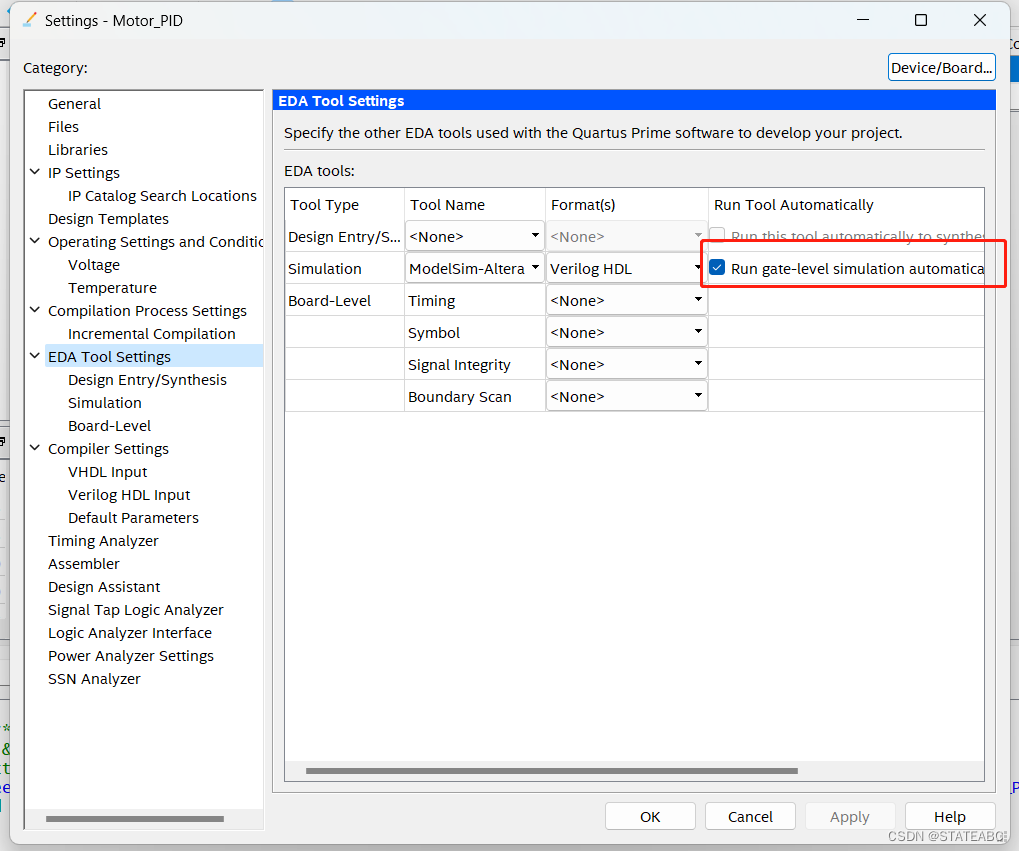

通过quartus启动modelsim-altera仿真时出现nativelink error-couldn‘t execute invalid argument的问题

问题截图 目前在百度中还没有人回答过这个问题,只能自己动手了.经排查,是因为在modelsim属性中曾将其设置为以管理员身份运行 将"以管理员身份运行此程序"取消即可. 亲测有效

FPGA微型板Verilog定时蜂鸣

您将基于通用的display_7_seg,decoder_7_seg和debouncer模块构建一个倒数计时器,其功能实际上类似于真实产品。 即使是表面上看似简单的设备(如计时器)也可能难以设计。 为了简化设计,通常使用称为状态机的表示。 该技…

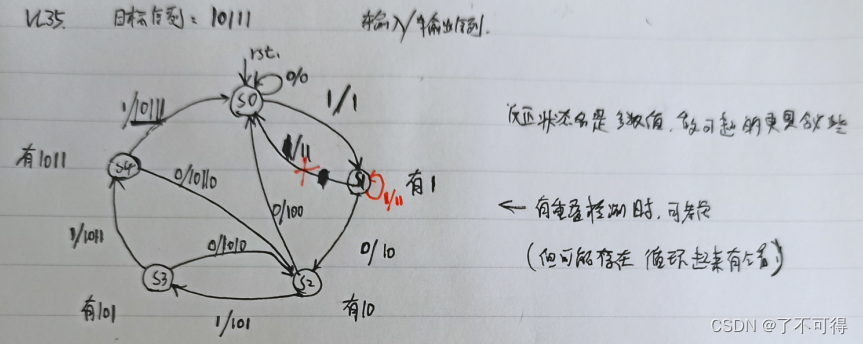

HDLBits学习------Problem 138~150

参考链接:HDLBits导学 Problem 138 Q8: Design a Mealy FSM 问题:实现一个Mealy类型的有限状态机,识别序列“101”,输入信号为x 。您的 FSM 应该有一个输出信号z,当检测到“101”序列时,该信号输出逻辑 1。…

FPGA驱动OLED Verilog代码 (三)------ 顶层模块 点亮OLED

一、代码 顶层模块比较简单,直接实例化各个模块进行连接就好了,下载程序到板子是哪个后,现象应该是整个OLED屏被填满

代码如下:

module oled_drive(input clk, //时钟信号 50MHzinput rst_n, //按键复位output oled_rst, //o…

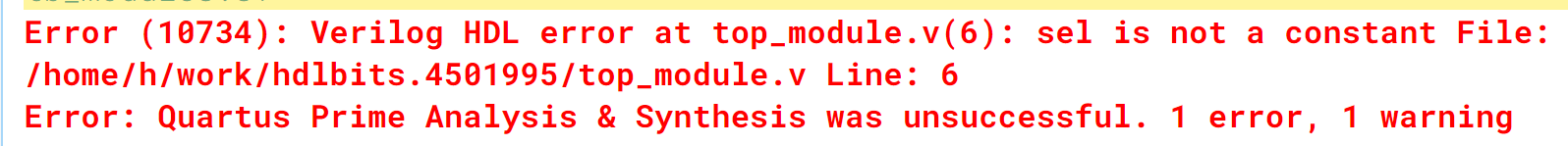

HDLBits学习------Problem 158~162

参考连接:HDLBits导学 Problem 158 Mux 问题:这个 8 位宽的 2 选 1 选择器不起作用。修复错误 原代码:

module top_module (input sel,input [7:0] a,input [7:0] b,output out );assign out (~sel & a) | (sel & b);endmodule 解…

HDLBits学习------Problem 163~172

Problem 163 Combinational circuit 1 问题:通过仿真波形实现电路 思路:通过波形可以看出来是一个与门 解决:

module top_module (input a,input b,output q );//assign q a & b; // Fix meendmodule居然一开始看成了同或门 Problem 16…

FPGA驱动OLED Verilog代码 (二)------ OLED初始化

一、概述: 逐字节发送初始化命令给OLED,设置OLED的一些寄存器。当然,我自己肯定也没有去研究过应该发哪些命令(毕竟用32的使用都是直接copy的代码),然后现在也是参照之前32驱动OLED的初始化命令来实现OLED的…

HDLBits学习------Problem 173~177(完结)

Problem 173 Clock 问题:编写testbench产生一个驱动时钟信号,来驱动模块dut,时钟周期为10ps 解决:

timescale 1ps/1ps //仿真单位为1ps,精度为1ps

module top_module ( );reg clk;dut dut_inst(clk);initial begin#0 …

HDLBits学习------Problem 151~157

参考链接:HDLBits导学 Problem 151 Counter with period 1000 问题:构建一个从 0 到 999(包括 0 到 999)计数的计数器,周期为 1000 个周期。复位输入是同步的,应将计数器复位为 0 解决:

module…

Circuits--Sequential Logic--Shift Registers--Exams/m2014 q4k

网址:https://hdlbits.01xz.net/wiki/Exams/m2014_q4k 自己写:

module top_module (input clk,input resetn, // synchronous resetinput in,output out);reg r_in1;reg r_in2;reg r_in3;always(posedge clk)beginif(resetn 1b0)begin …

Circuits--Sequential Logic--More Circuits--Conwaylife

网址:https://hdlbits.01xz.net/wiki/Conwaylife

module top_module(input clk,input load,input [255:0] data,output [255:0] q ); reg [323:0] data_padding; //18*18wire [255:0] q_next;integer i,j,neighbour_cnt;always (*)begin//paddingdata_padding[17:0…

Circuits--Sequential Logic--Counters--Countbcd

网址:https://hdlbits.01xz.net/wiki/Countbcd

module bcdcount

( input clk,input reset,input ena,output reg [3:0] q

);always (posedge clk)beginif (reset 1b1)q < 4b0;else if (ena 1b1)beginif (q 4h9)q < 4b0;elseq < q 1b1 ; endend

endmo…

Circuits--Sequential Logic--Finite State Machines--Fsm1s

网址:https://hdlbits.01xz.net/wiki/Fsm1s

// Note the Verilog-1995 module declaration syntax here:

module top_module(clk, reset, in, out);input clk;input reset; // Synchronous reset to state Binput in;output out;// reg out;// Fill in state name declar…

FPGA驱动LCD1602(IIC) Verilog代码(四)------ 顶层模块

一、概述 顶层模块就是例化lcd初始化模块和写命令/数据模块,然后把两个模块连接起来就完成了 先贴一下最后实现的效果图 顶层模块代码如下 二、Verilog代码

module lcd_drive(input clk, //时钟信号 50minput rst_n, //按键复位output scl, //iic sclinout sda …

Circuits--Sequential Logic--Finite State Machines--Fsm2

网址:https://hdlbits.01xz.net/wiki/Fsm2

module top_module(input clk,input areset, // Asynchronous reset to OFFinput j,input k,output out); // parameter OFF=0, ON=1; reg state, next_state;always @

Circuits--Sequential Logic--Finite State Machines--Fsm1

网址:https://hdlbits.01xz.net/wiki/Fsm1

module top_module(input clk,input areset, // Asynchronous reset to state Binput in,output out);// parameter A=1b0;parameter B=1b1; reg state, next_state;always @(

FPGA微型板Verilog简单音频

简单音调生成

该模块通过使用一个计数器生成一个1 kHz的信号,该计数器在CLK的每个刻度上都递增。 当计数器达到32,000时,将切换输出BUZZER,并将计数器重置为0。

音频输出

使用一个1-kΩ电阻器和一小段实心线将GPIO引脚P97和GND连接到与有源…

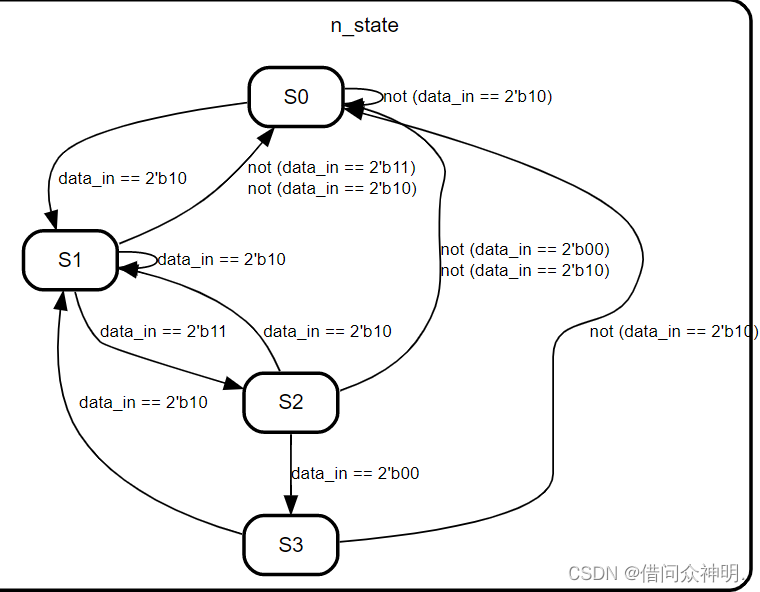

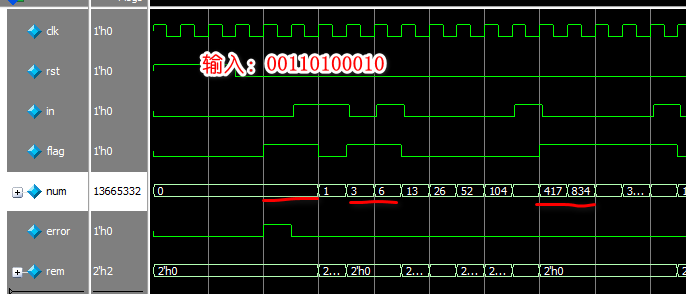

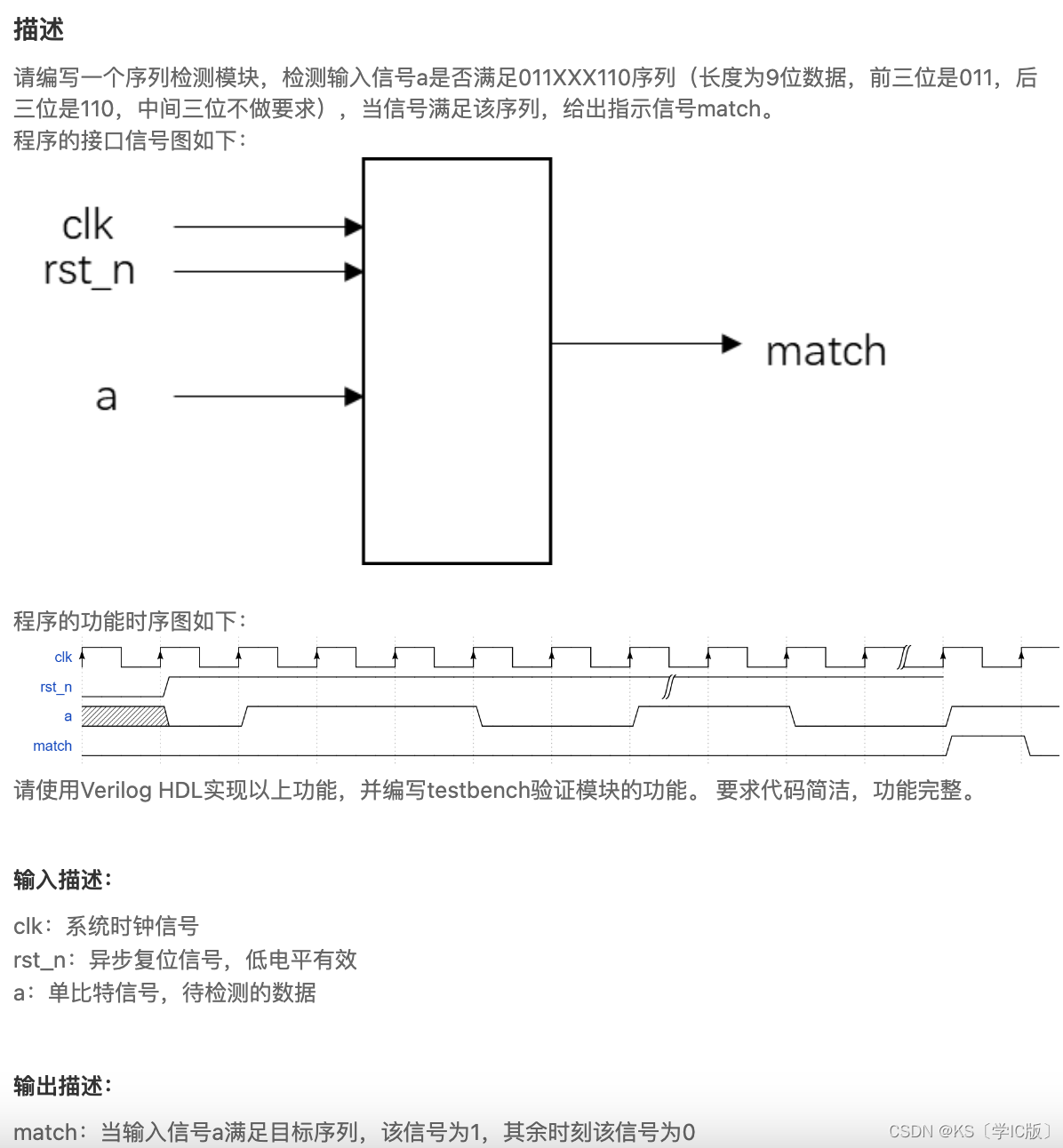

【24】Verilog进阶 - 序列检测2

VL35 状态机-非重叠的序列检测

1 思路

状态机嘛,也是比较熟悉的朋友啦, 我就火速写出了STG。如下黑色所示: 2 初版代码

`timescale 1ns/1nsmodule sequence_test1(input wire clk ,input wire rst ,input wire data ,output reg flag

);

//*************code**********…

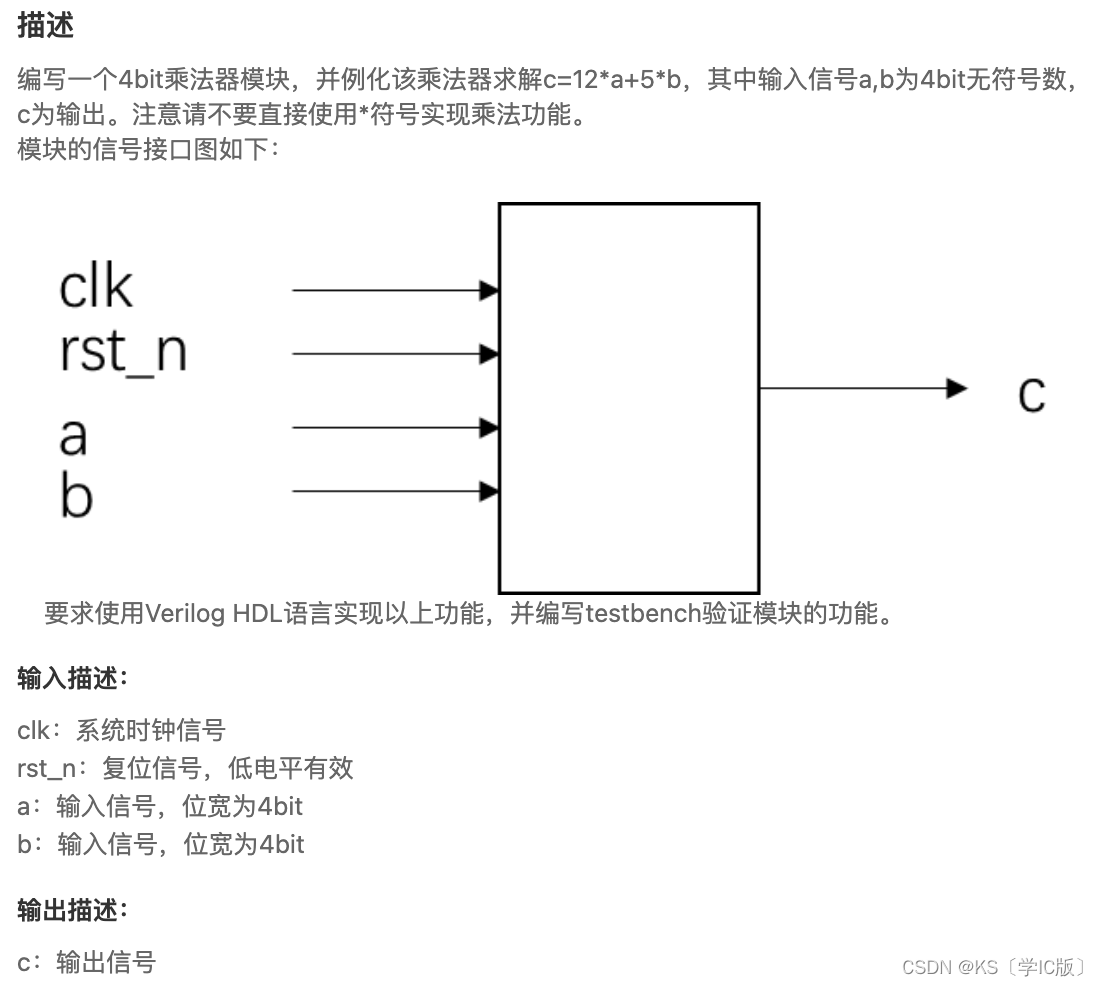

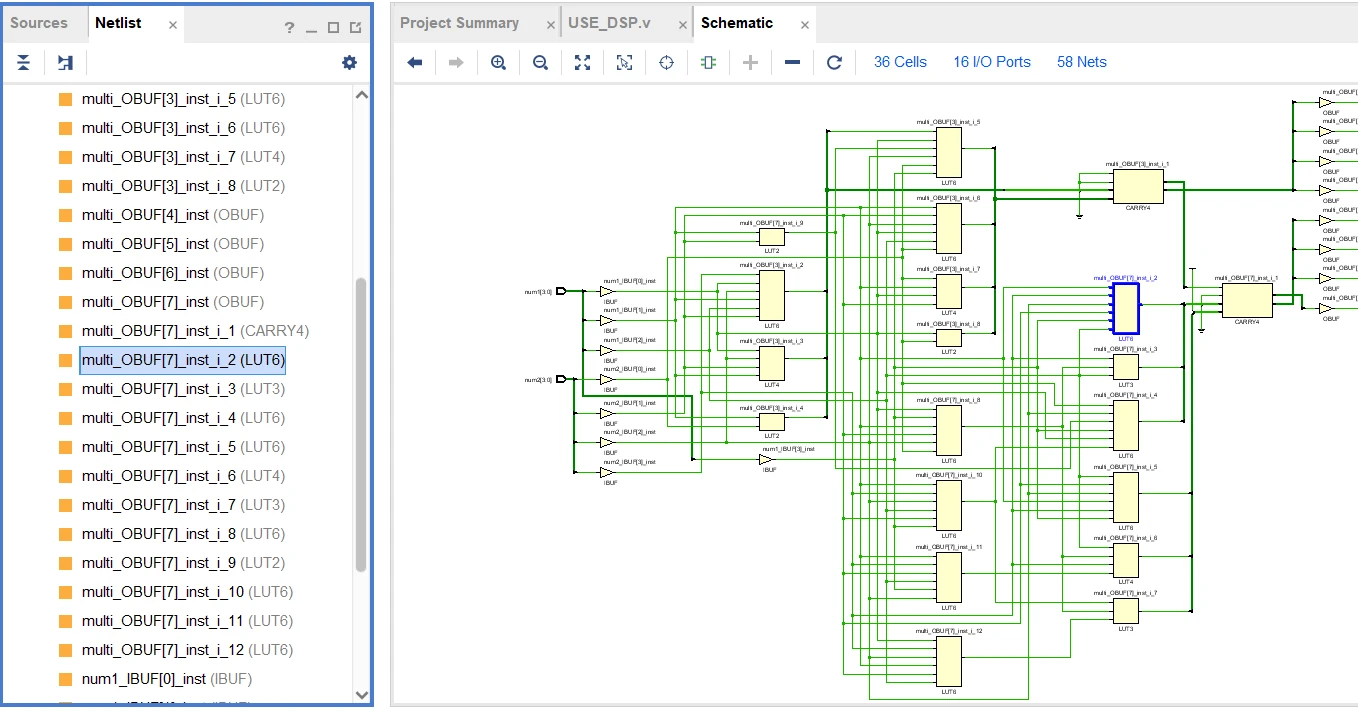

Verilog RTL 新手代码设计 (多路译码器、加法器、乘法器)

6.多路译码器

实现3-8译码器,使用case 语句实现,注意,一定要把case的情况写全,或者要加上default,代码如下:

// module top

module top(IN , // input OUT ); // output inp…

Verilog Language--More Verilog Features--Vector100r

网址:https://hdlbits.01xz.net/wiki/Vector100r

module top_module( input [99:0] in,output reg [99:0] out

); reg [99:0] i;alway

Verilog Language--Procedures--Always casez

网址:https://hdlbits.01xz.net/wiki/Always_casez

// synthesis verilog_input_version verilog_2001

module top_module (input [7:0] in,output reg [2:0] pos );always(*)begincasez(in[7:0])8bzzzzzzz1: pos 3d0;8bzzzzzz1z: pos 3d1;8bzzzzz1zz: pos 3d2…

Verilog Language--Procedures--Always nolatches

网址:https://hdlbits.01xz.net/wiki/Always_nolatches

// synthesis verilog_input_version verilog_2001

module top_module (input [15:0] scancode,output reg left,output reg down,output reg right,output reg up ); always@(*)begincase

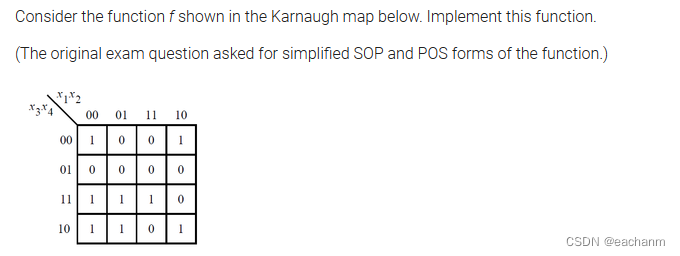

Circuits--Combinational Logic--Karnaugh Map to Circuit--Kmaps

网址:https://hdlbits.01xz.net/wiki/Kmap3#

module top_module(input a,input b,input c,input d,output out ); assign out a | (~b & c); //b为无关项endmodule

Verilog Language--Modules:Hierarchy--Module pos

网址:https://hdlbits.01xz.net/wiki/Module_pos

module top_module ( input a, input b, input c,input d,output out1,output out2

);mod_a mod_a(out1,out2,a,b,c,d);endmodule

Circuits--Sequential Logic--Shift Registers--Rotate 100

网址:https://hdlbits.01xz.net/wiki/Rotate100

module top_module(input clk,input load,input [1:0] ena,input [99:0] data,output reg [99:0] q); always(posedge clk)beginif(load 1b1)q < data;else begincase(ena)2b01: q < {q[0],q[99:1]};2b10: q …

HDLBits:在线学习 Verilog (十三 · Problem 60-64)

本系列内容来自于知乎专栏,链接如下:https://zhuanlan.zhihu.com/c_1131528588117385216本系列文章将和读者一起巡礼数字逻辑在线学习网站 HDLBits 的教程与习题,并附上解答和一些作者个人的理解,相信无论是想 7 分钟精通 Verilog…

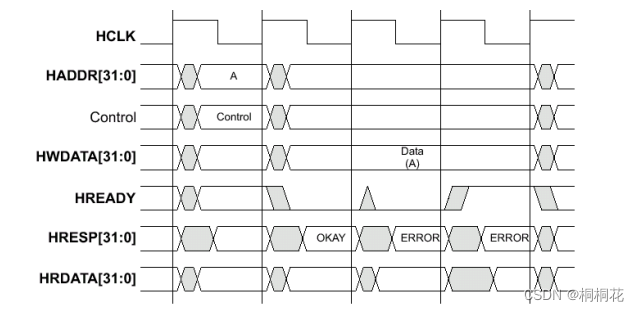

【转载】AXI4的传输事物结构(transaction structure)

前言:本来想自己写这一部分,但是发现网上已经有人详细写过了,那么我就转载两篇,以供自己或者大家未来学习与温故。

AXI4的传输事物结构 关于AHB总线回环突发 wrap burst模式地址的理解

---------------------------------------…

《Clock Domain Crossing》 翻译与理解(6)跨时钟域的命名规则与设计分割

本系列将对sunburst design网站的2008最佳文章《Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog》进行翻译和基于自我理解的分析阐述,本文介绍多信号跨时钟域传输。

时钟与信号命名

当一个整体设计中包含较多时钟时&…

Circuits--Sequential Logic--Shift Registers--Shift18

网址:https://hdlbits.01xz.net/wiki/Shift18

module top_module(input clk,input load,input ena,input [1:0] amount,input [63:0] data,output reg [63:0] q); always(posedge clk)beginif(load 1b1)q < data;else if(ena 1b1)begincase(amount)2b00: q &l…

Circuits--Sequential Logic--Latches and Flip-Flops--Dualedge

网址:https://hdlbits.01xz.net/wiki/Dualedge 第一种解法:

module top_module (input clk,input d,output q

);reg m = 1b0;reg n = 1b0;always@(posedge clk)beginm = d;end always@(negedge clk)

Circuits--Sequential Logic--Finite State Machines--Lemmings4

网址:https://hdlbits.01xz.net/wiki/Lemmings4

module top_module(input clk,input areset, // Freshly brainwashed Lemmings walk left.input bump_left,input bump_right,input ground,input dig,output walk_left,output walk_right,output aaah,output digging); pa…

Verilog Language--More Verilog Features--Bcdadd100

网址:https://hdlbits.01xz.net/wiki/Bcdadd100

module top_module( input [399:0] a, b,input cin,output cout,output [399:0] sum );reg ci,co;reg

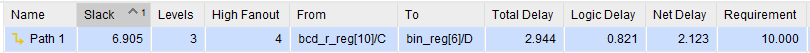

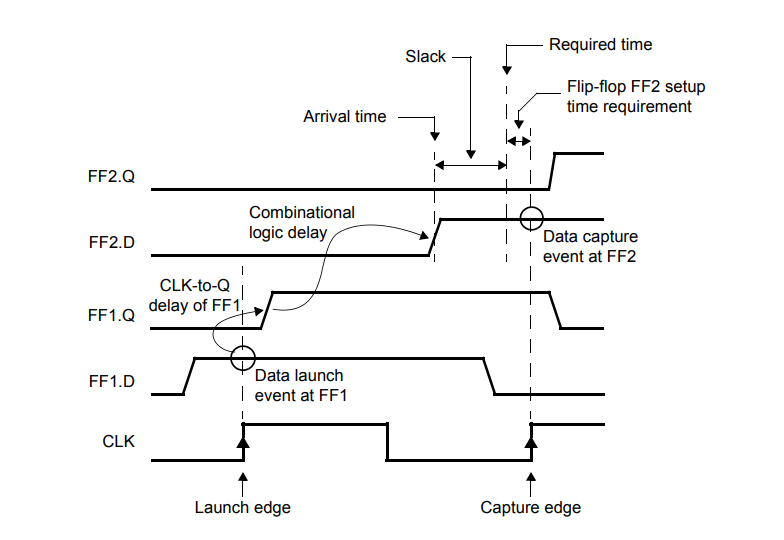

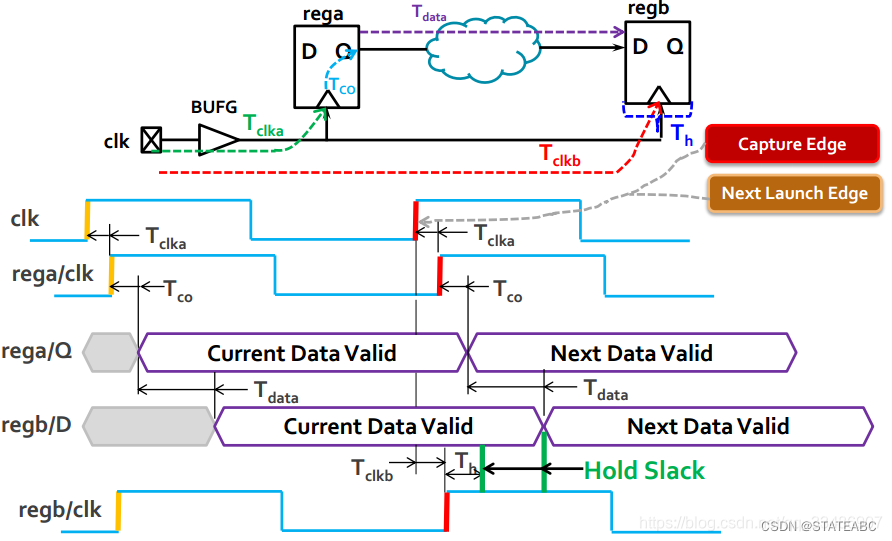

静态时序分析(原理最清晰版本)

前言:看了非常多静态时序分析的博客和文章,觉得大部分是云里雾里,很多人在照本宣科,所以我决定完全用自己的理解,用人话来写一篇,静态分析的原理是什么。

定义:

摘录自维基百科

建立时间&…

FPGA微型板Verilog实现PWM和伺服电机

PWM介绍

下图显示了PWM的工作原理。 如果脉冲很短(例如,仅在5%的时间内为高),则每个脉冲仅传递少量能量。 脉冲越长,向负载提供的能量就越多。 在为电动机供电时,这将控制电动机的旋转速度。 使…

Circuits--Aequential Logic--Latches and Flip-Flops--Dff16e

网址:https://hdlbits.01xz.net/wiki/Dff16e

module top_module (input clk,input resetn,input [1:0] byteena,input [15:0] d,output [15:0] q

)<

Circuits--Swquential Logic--Shift Registers--Shift4

网址:https://hdlbits.01xz.net/wiki/Shift4

module top_module(input clk,input areset, // async active-high reset to zeroinput load,input ena,input [3:0] data,output reg [3:0] q); always(posedge clk or posedge areset)beginif(areset 1b1)q < 4d…

Circuits--Sequential Logic--More Circuits--Rule110

网址:https://hdlbits.01xz.net/wiki/Rule110

module top_module(input clk,input load,input [511:0] data,output [511:0] q

); reg [511:0] q_l;reg [511:0] q_r;assign q_l {1b0, q[511:1]};assign q_r {q[510:0] , 1b0};always(posedge clk)beginif (load…

Circuits--Combinational Logic--Basic Gates--Gatesv100

网址:https://hdlbits.01xz.net/wiki/Gatesv100

module top_module( input [99:0] in,output [98:0] out_both,output [99:1] out_any,output [99:0] out_different );assign out_both in[98:0] & in[99:1];assign out_any in[99:1] | in[98:0];assign out_d…

Circuits--Sequential Logic--Finite State Machines--Fsm3s

网址:https://hdlbits.01xz.net/wiki/Fsm3s

module top_module(input clk,input in,input reset,output out); //parameter A=0, B=1, C=2, D=3;reg

Verilog Language--Modules:Hierarchy--Module cseladd

网址:https://hdlbits.01xz.net/wiki/Module_cseladd module top_module(input [31:0] a,input [31:0] b,output [31:0] sum

);wire SW

Circuits--Basic Gates--Popcount3

网址:https://hdlbits.01xz.net/wiki/Popcount3

module top_module( input [2:0] in,output [1:0] out );//assign out in[0]in[1]in[2];assign out[0] in[0]^in[1]^in[2];assign out[1] in[0]&in[1] | in[0]&in[2] | in[1]&in[2];endmodule

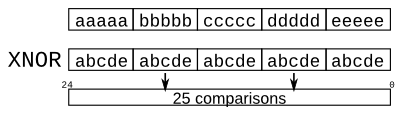

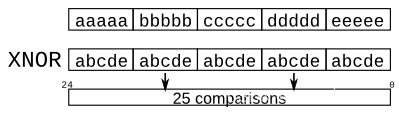

Verilog Language--Vectors--Vector5

网址:https://hdlbits.01xz.net/wiki/Vector5

module top_module (input a, b, c, d, e,output [24:0] out );//// The output is XNOR of two vectors created by // concatenating and replicating the five inputs.assign out ~{{5{a}},{5{b}},{5{c}},{5{d}},{…

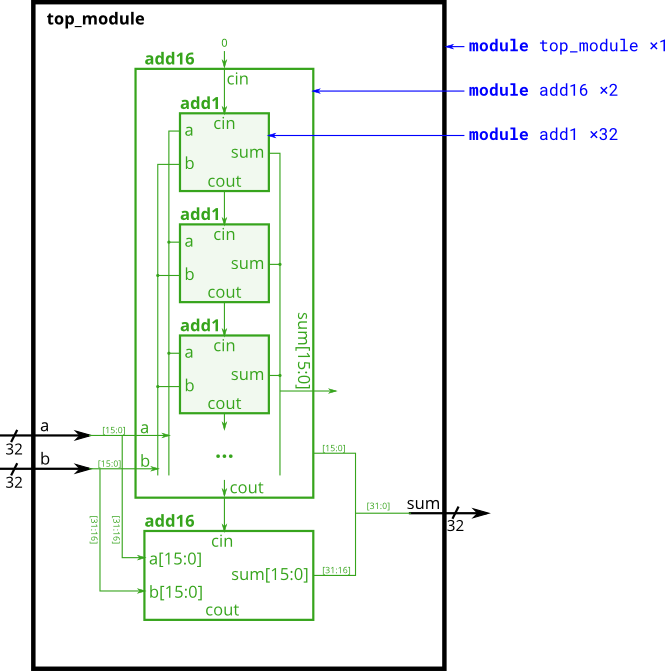

Verilog Language--Modules:Hierachy--Module add

网址:https://hdlbits.01xz.net/wiki/Module_add

module top_module(input [31:0] a,input [31:0] b,output [31:0] sum

);reg r_cout;reg [15:0] sum1;reg [15:0] sum2;add16 add16_inst1(.a (a[15:0] ),.b (b[15:0] ),.cin(1b0), .sum (sum1 ),.cout(r_cout) )…

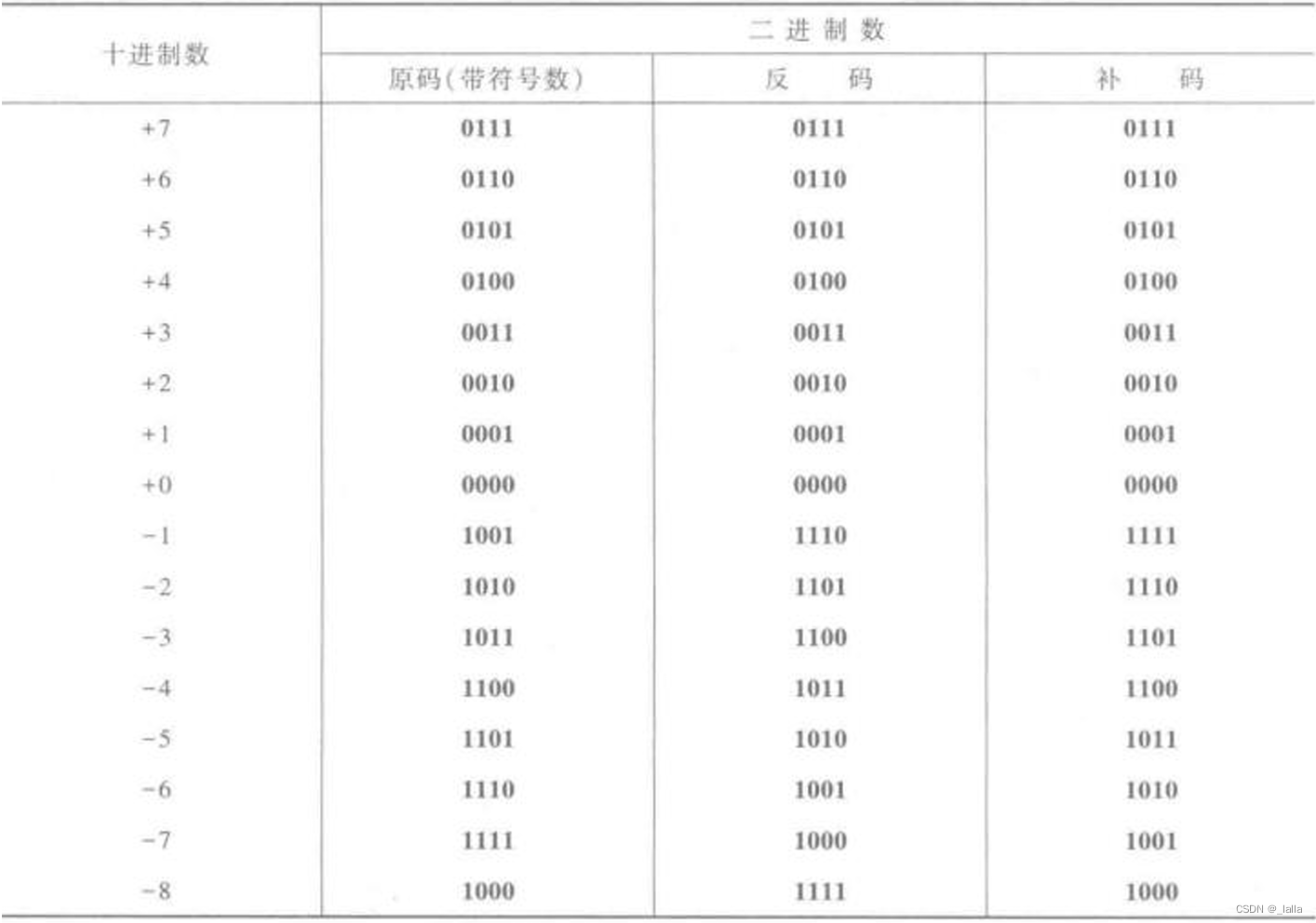

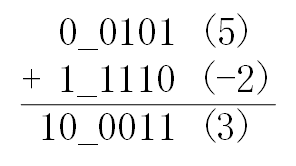

verilog学习笔记5——进制和码制、原码/反码/补码

文章目录 前言一、进制转换1、十进制转二进制2、二进制转十进制3、二进制乘除法 二、原码、反码、补码1、由补码计算十进制数2、计算某个负数的补码 前言

2023.8.13 天气晴 一、进制转换

1、十进制转二进制

整数:除以2,余数倒着写 小数:乘…

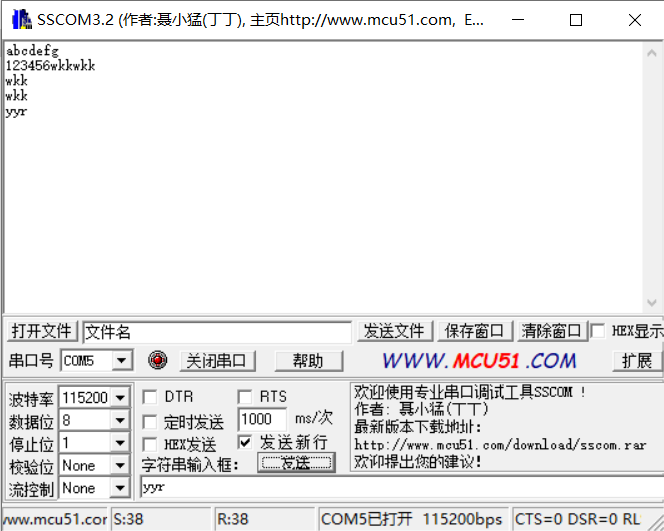

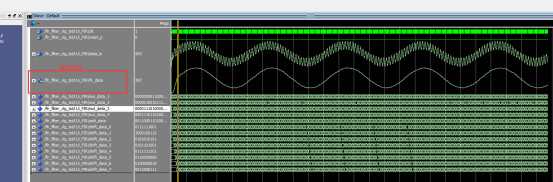

FPGA之手把手教你写串口协议解析(STM32与FPGA数据互传)

文章目录 博主的念叨一、任务介绍1、本文目标2、设计思路3、设计注意事项 二、设计代码1.串口接收代码2.串口发送代码3.串口解析代码4.顶层代码 总结 博主的念叨

最近趁热打铁做了一个关于STM32与FPGA通信并且控制高速DA模块产生不同频率信号的正弦波、方波、三角波和锯齿波的…

Verilog Language--Modules:Hierarchy--Module fadd

网址:https://hdlbits.01xz.net/wiki/Module_fadd module top_module (input [31:0] a,input [31:0] b,output [31:0] sum

);//

add16 add16

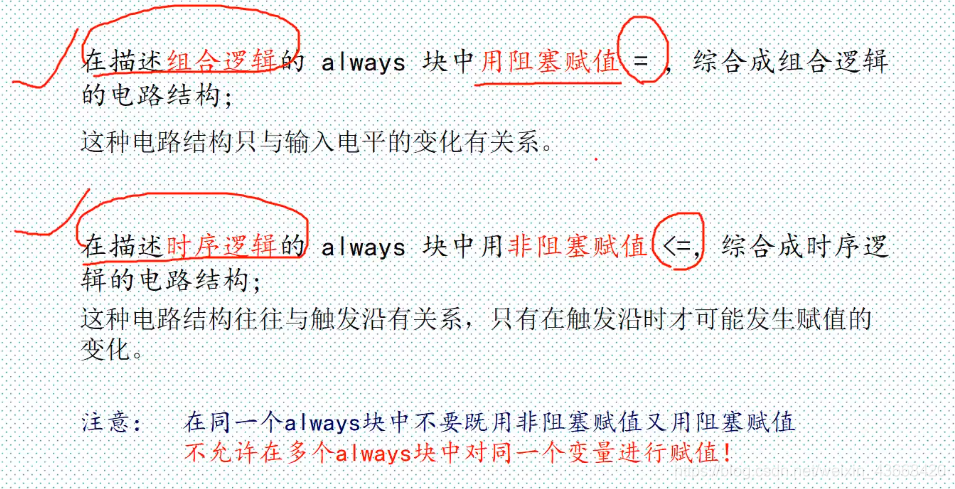

阻塞赋值和非阻塞赋值的区别

1、阻塞赋值 是顺序执行的,上面一条语句执行完之后,再执行下一行语句,如下图所示:

2、非阻塞赋值 第一行语句执行的时候,并不阻止下面语句的执行,并行执行。如下图所示: 3、使用方法

FPGA驱动LCD1602(IIC) Verilog代码(二)------ LCD写命令/数据模块

一、概述 时序及数据参考链接:51单片机 使用IIC转接板驱动LCD1602 lcd1602引脚说明参考链接:STM32通过(软/硬IIC)控制LCD1602液晶显示屏(IIC转8位并口的PCF8574转接板的使用)原创 (图片来自上述…

FPGA驱动LCD1602(IIC) Verilog代码(一)------ IIC写模块

一、概述 IIC时序参考链接:51单片机 使用IIC转接板驱动LCD1602 基本参考该链接中的IIC时序,使用Verilog代码来实现IIC写模块。只是比较好奇为什么在所有位发完之后,scl还要拉低再拉高了(我没有这样做的时候会一直收不到ack信号&am…

Verilog频率计设计

数字频率计的基本设计思路是在给定一个time开始测量的时候产生的T的个数,也就是采用一个标准的基准时钟,在单位时间(1秒)里对被测信号的脉冲数进行计数。测频法包括直接测频法、等精度频率测量法、周期法等。 数字频率计的原理如图…

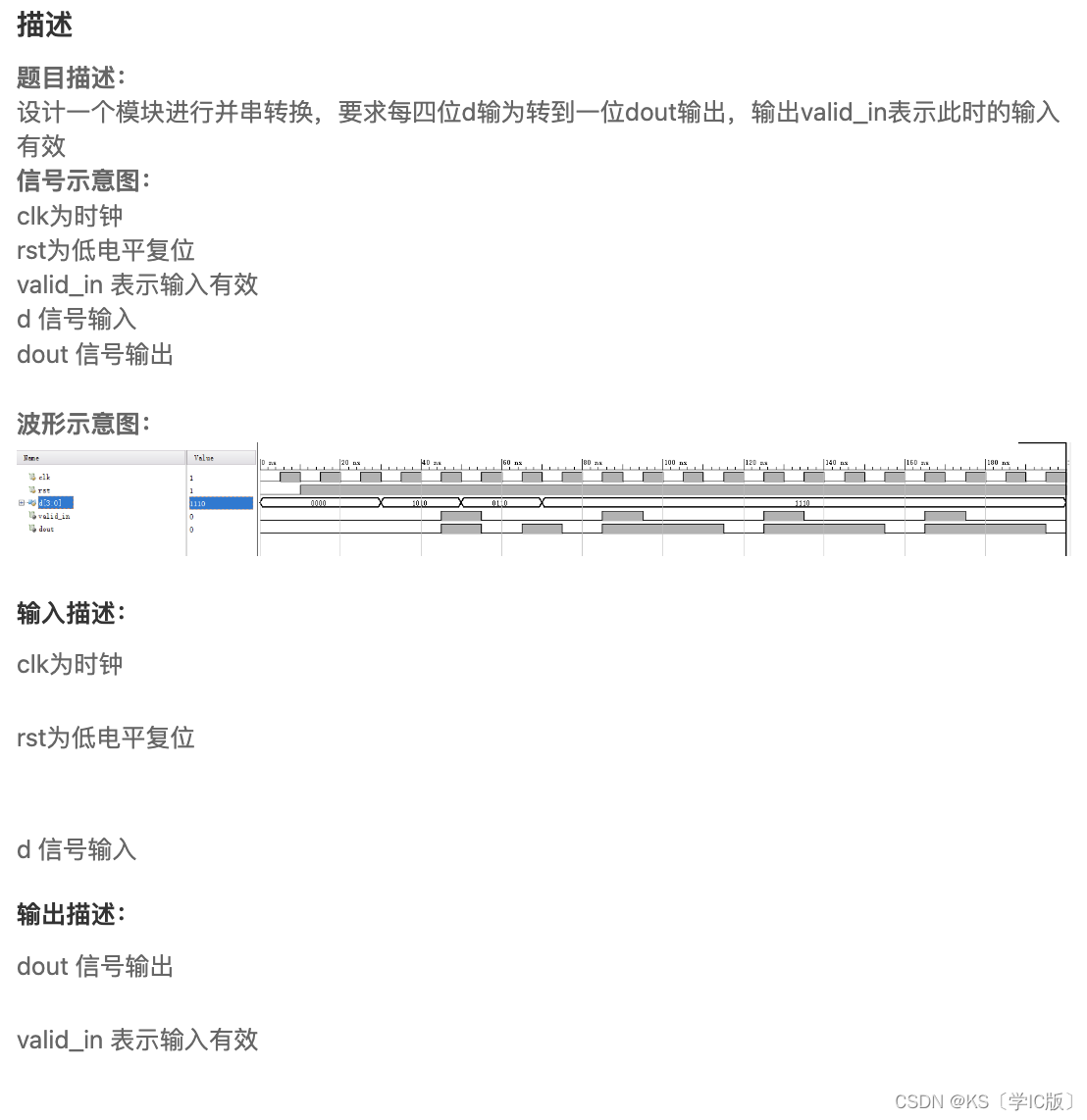

「Verilog学习笔记」并串转换

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 串并转换操作是非常灵活的操作,核心思想就是移位。串转并就是把1位的输入放到N位reg的最低位,然后N位reg左移一位,在把1位输入放到左移后…

《Clock Domain Crossing》 翻译与理解(1)亚稳态

前言:本系列将对sunburst design网站的2008最佳文章《Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog》进行翻译和基于自我理解的分析阐述,本文先介绍亚稳态。

亚稳态

亚稳性是指在设计的正常操作过程中的某个…

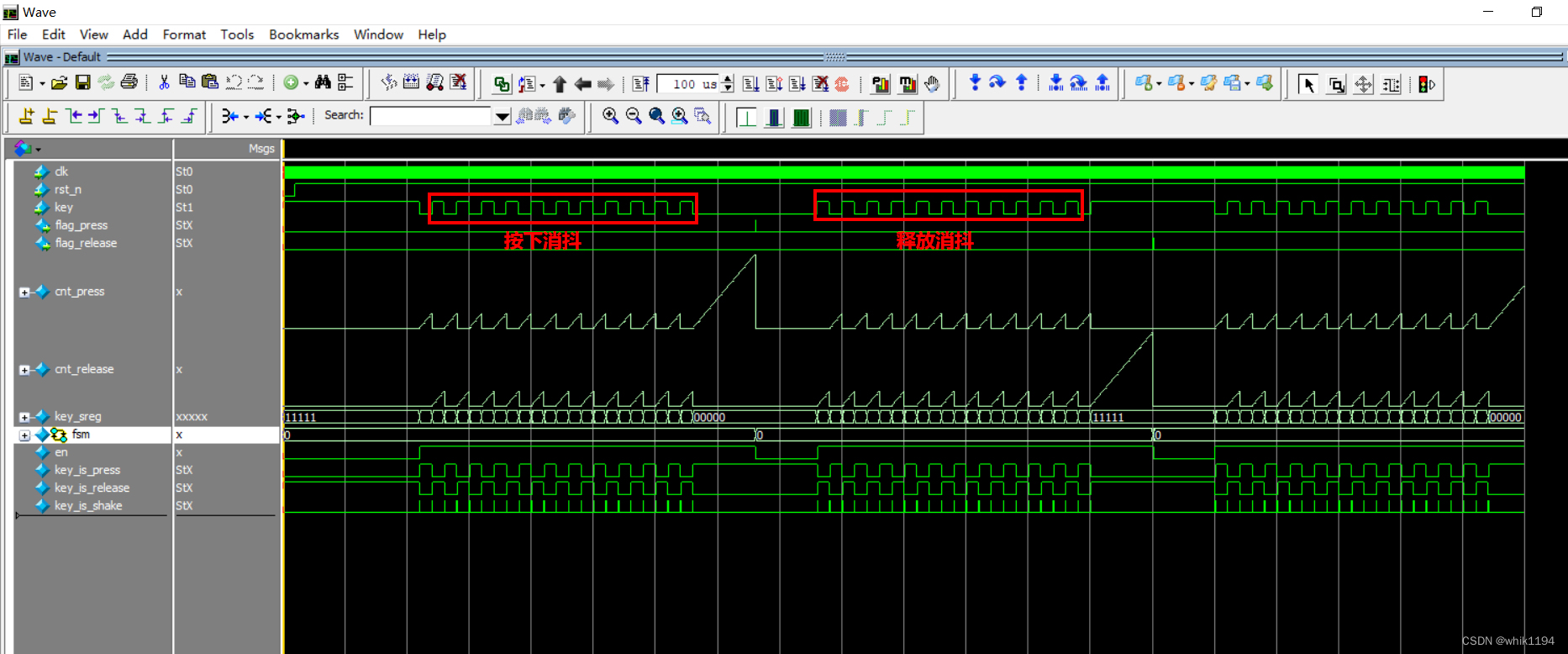

FPGA——按键消抖常用模板代码

模板如下:

//define UD #1

module key_jitter(input clkin,input key_in,output key_value// output [15:0] tout

);// inner signal

reg [1:0] key_in_r;

wire pp;

reg [19:0] cnt_base;

reg key_value_r;always (posedge clkin)key_in_…

用verilog实现斐波那契数列发生器

斐波那契数列(0,1,1,2,3,5,8,13…)

思路很简单,只用两个寄存器,根据斐波那契数列的特点,每次时钟到来时,把reg2赋值给reg1,把reg1和reg2相加赋值给reg2。因为是非阻塞赋值,不用额外…

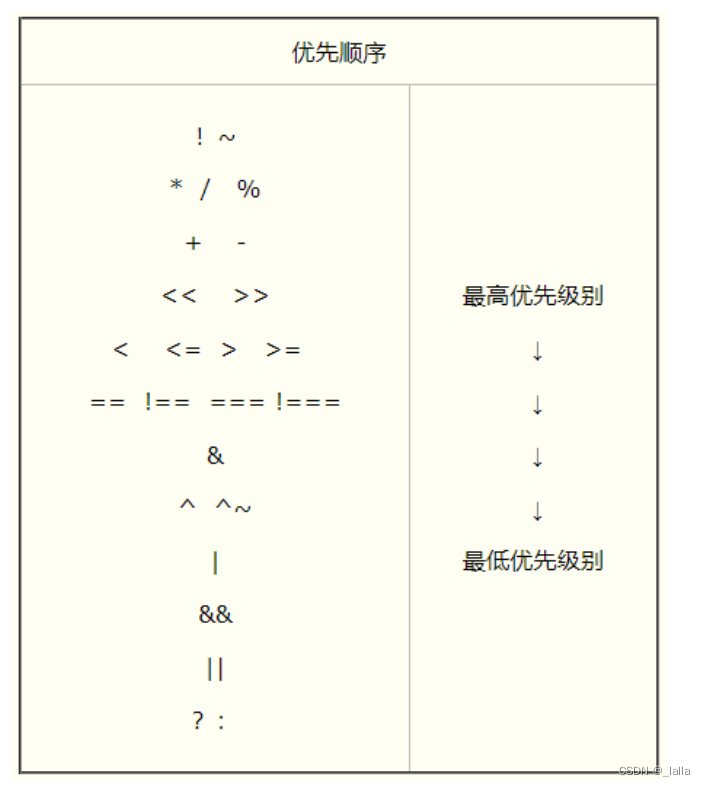

[Verilog] Verilog 基本格式和语法

主页: 元存储博客 全文 3000 字 文章目录 1. 声明格式1.1 模块声明1.2 输入输出声明1.3 内部信号声明1.4 内部逻辑声明1.5 连接声明1.6 数据类型声明1.7 运算符和表达式1.8 控制结构 2. 书写格式2.1 大小写2.2 换行2.3 语句结束符2.4 注释2.5 标识符2.6 关键字 1. 声…

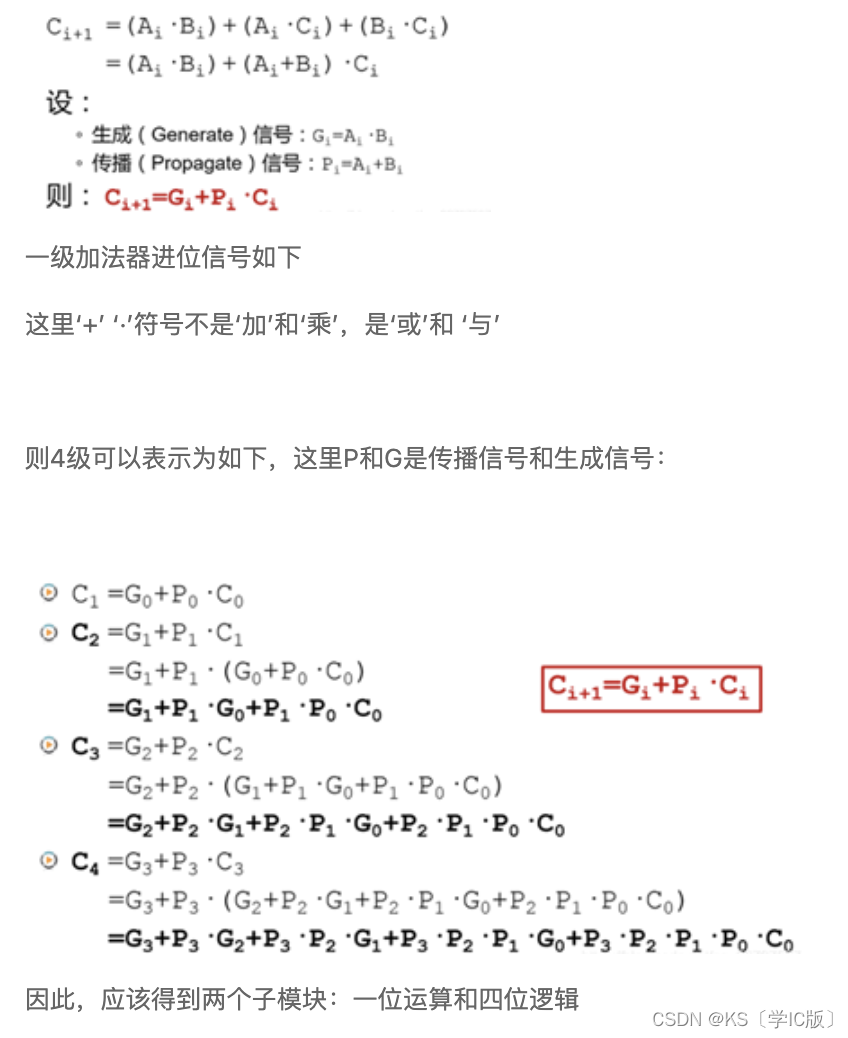

「Verilog学习笔记」4bit超前进位加法器电路

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 分析 timescale 1ns/1nsmodule lca_4(input [3:0] A_in ,input [3:0] B_in ,input C_1 ,output wire CO ,output wire [3:0] …

Vivado如何清理工程,并避免缺失必要的文件?

FPGA开发是一项非常复杂的工作,需要处理大量的代码、约束和仿真文件。在开发过程中,由于文件数量庞大,很容易导致工程变得混乱不堪。Vivado是Xilinx公司推出的一款FPGA开发工具,能够帮助开发人员处理这种复杂性,提高开…

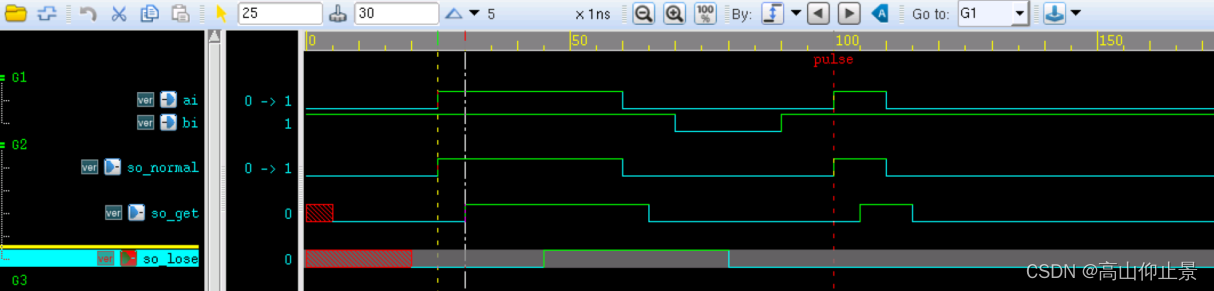

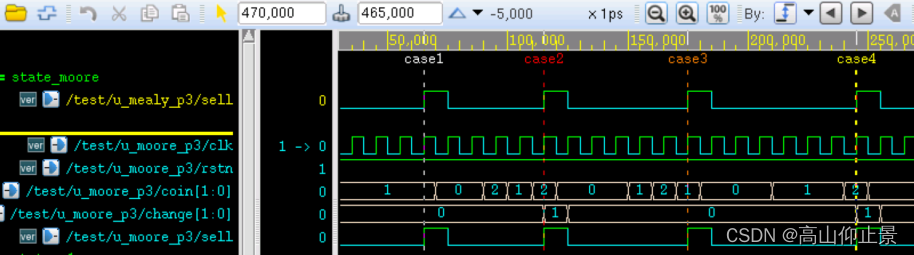

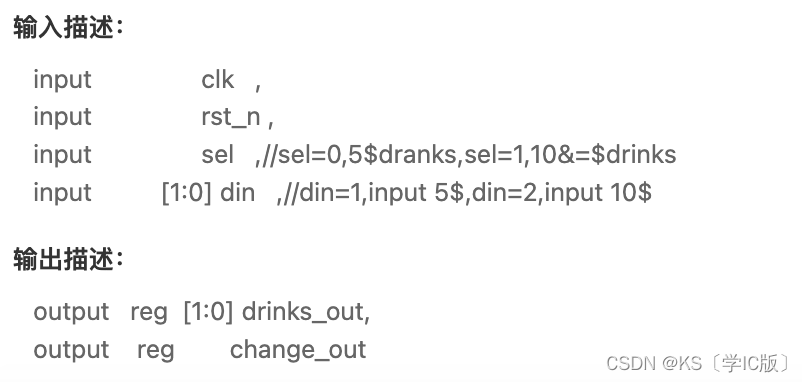

【26】Verilog进阶 - 自动贩卖机【SO EASY】

VL38 自动贩售机1

一把过,没啥说的

1 题目 (1)题目描述: 设计一个自动贩售机,输入货币有三种,为0.5/1/2元,饮料价格是1.5元,要求进行找零,找零只会支付0.5元。 ps: 投入的货币会自动经过边沿检测并输出一个在时钟上升沿到1,在下降沿到0的脉冲信号 注意rst为低电平复…

《计算机组成与CPU设计实验》4 时序逻辑(三)

计数器

逻辑功能

对输入时钟脉冲进行计数也可用于分频、定时、产生节拍脉冲等

分类

按时钟输入方式,分为同步和异步计数器按进位体制,分为二进制、十进制和任意进制计数器按计数方向,分为加法、减法和可逆计数器

计数器的“模”(Modulo) 计…

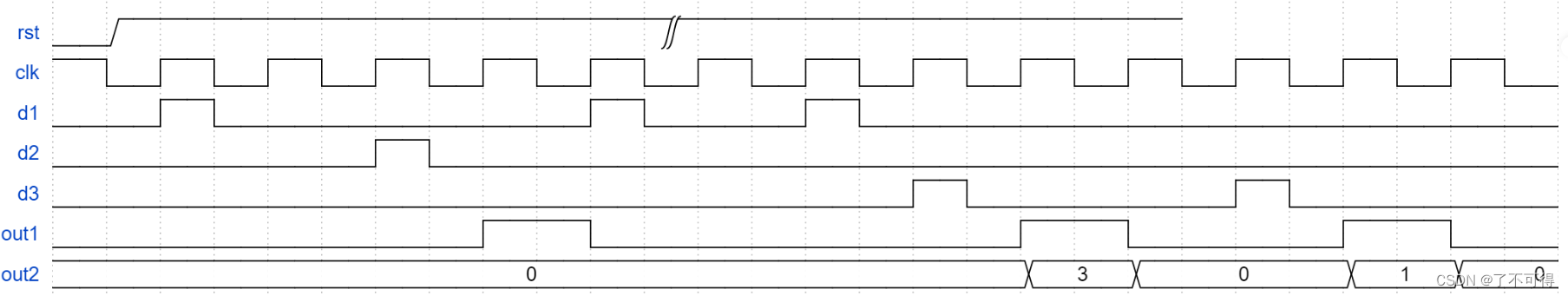

「Verilog学习笔记」边沿检测

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 timescale 1ns/1ns

module edge_detect(input clk,input rst_n,input a,output reg rise,output reg down

);reg a_tem ; always (posedge clk or negedge rst_n) beginif…

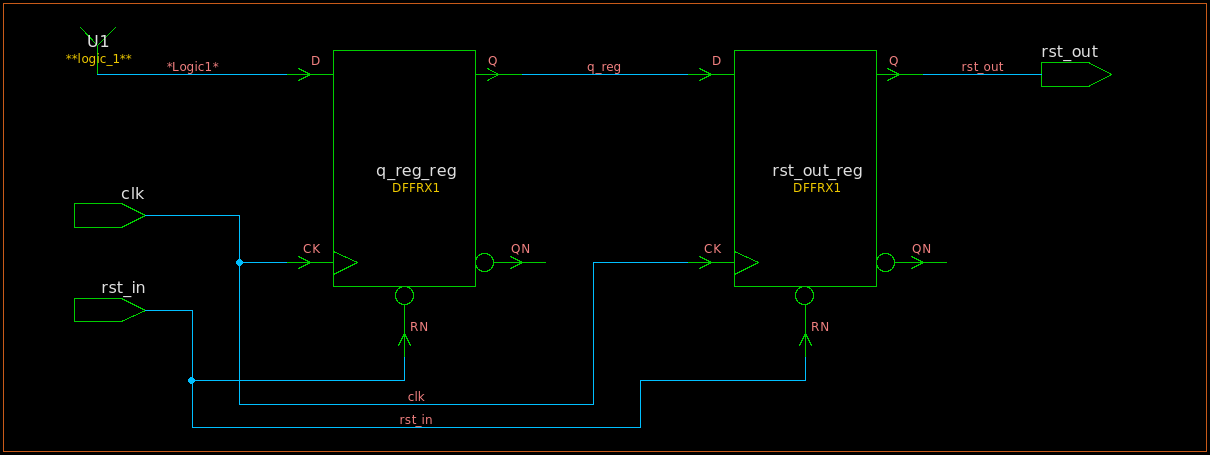

异步复位同步释放的理解

文章目录同步复位异步复位异步复位,同步释放同步复位

在同步复位中,复位信息的传递由时钟信号控制,仅当时钟上升沿到来时才会将复位信息和数据d存入寄存器中。电路图如下: 同步复位优缺点:

确保电路为同步的减少毛刺…

牛客网Verilog刷题 | 入门特别版本

文章目录 1、 VL1 输出12、VL2 wire连线3、 VL3 多wire连接4、VL4 反相器5、VL5 与门6、VL6 NOR 门7、VL7 XOR 门8、VL8 逻辑运算10、VL10 逻辑运算211、VL11 多位信号12、VL12 信号顺序调整13、VL13 位运算与逻辑运算14、VL14 对信号按位操作15、VL15 信号级联合并16、VL16 信…

Verilog RTL 面试题

最近在亚马逊上买了本verilog面试题的书,在这里把题目总结一下。 这是封面RTL verilog 语法问题

1 解释阻塞赋值和非阻塞赋值的区别与用法

2 解释逻辑运算符与按位运算符的区别

3 写出与、或、非、与非、或非、异或、同或(异或非)的RTL语句…

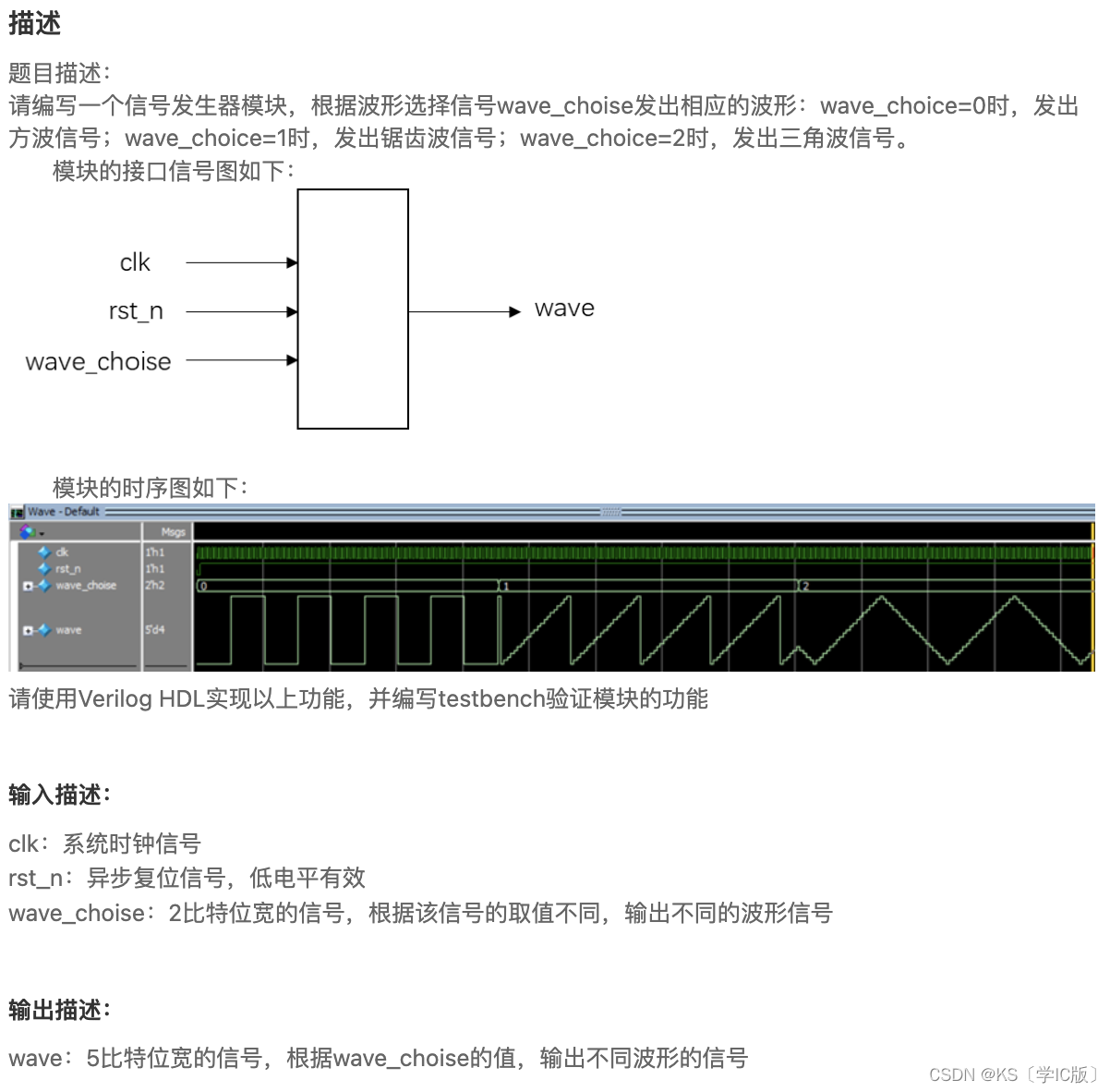

不同形状信号产生电路

题目描述:

编写一个信号发生器模块,根据波形选择信号wave_choise发出相应的波形:wave_choice0时,发出方波信号;wave_choice1时,发出锯齿波信号;wave_choice2时,发出三角波信号。

解…

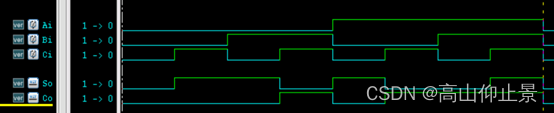

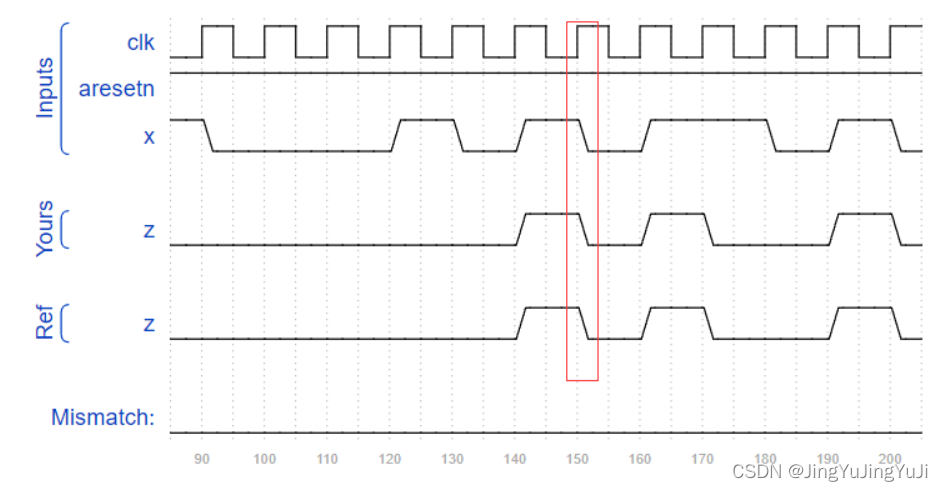

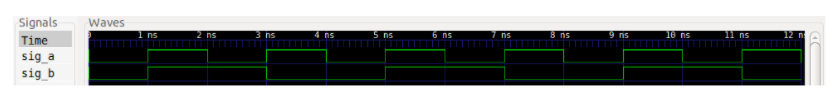

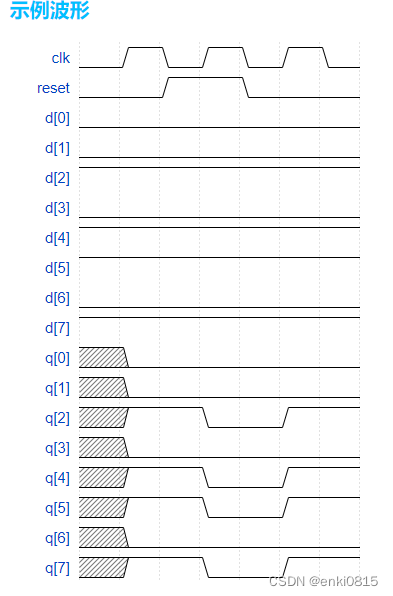

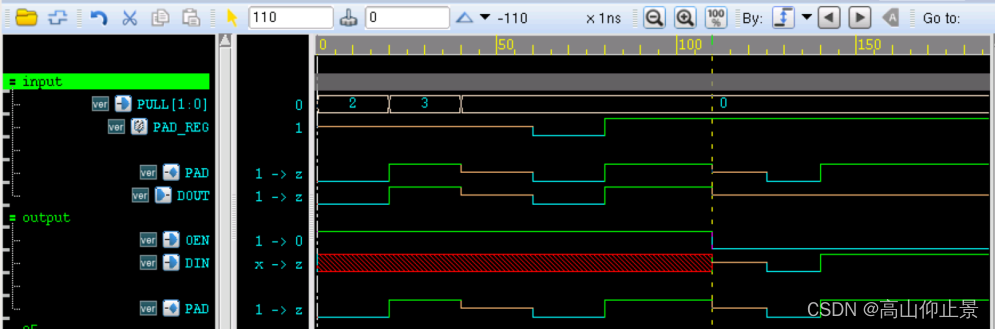

Edgedetect2

边缘检测,检查数据变化,用异或实现 对于 8 位矢量中的每个位,检测输入信号何时从一个时钟周期变为下一个时钟周期(检测任何边沿)。输出位应在发生 0 到 1 转换后设置周期。

以下是一些示例。为清楚起见,in…

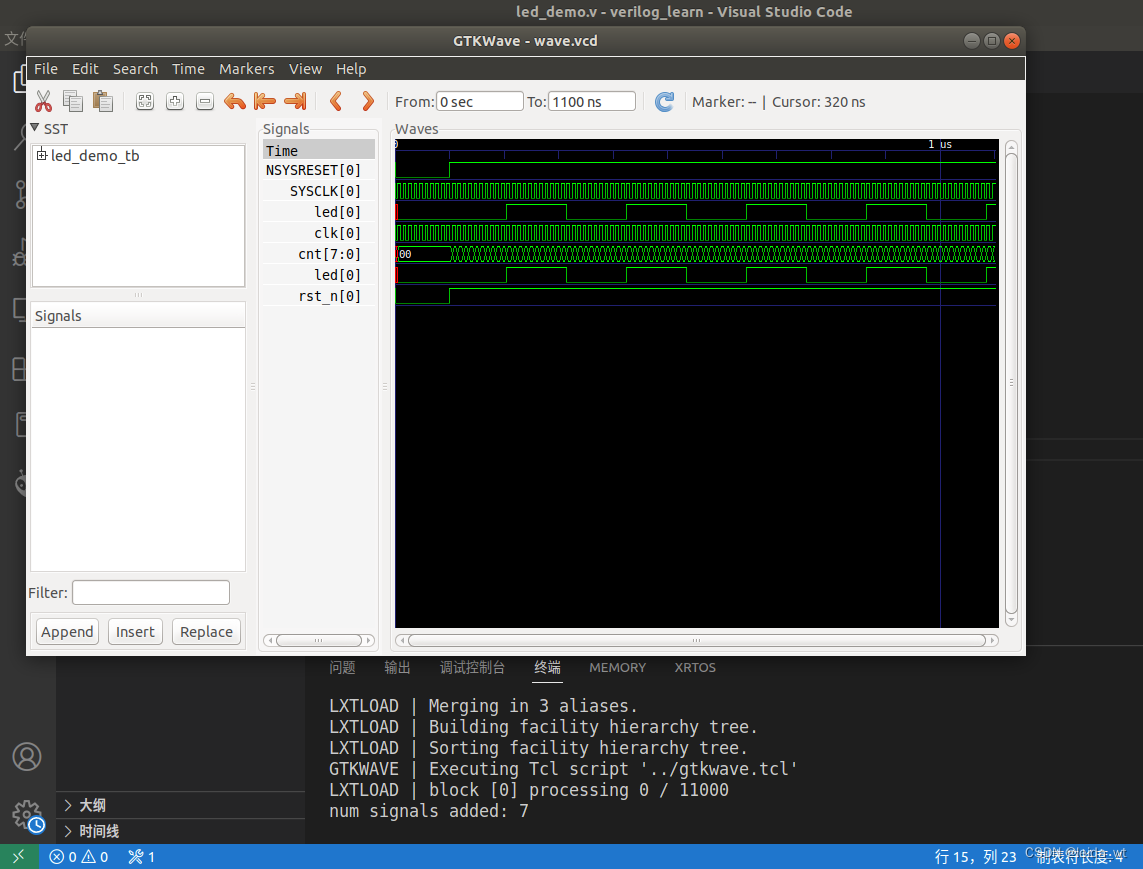

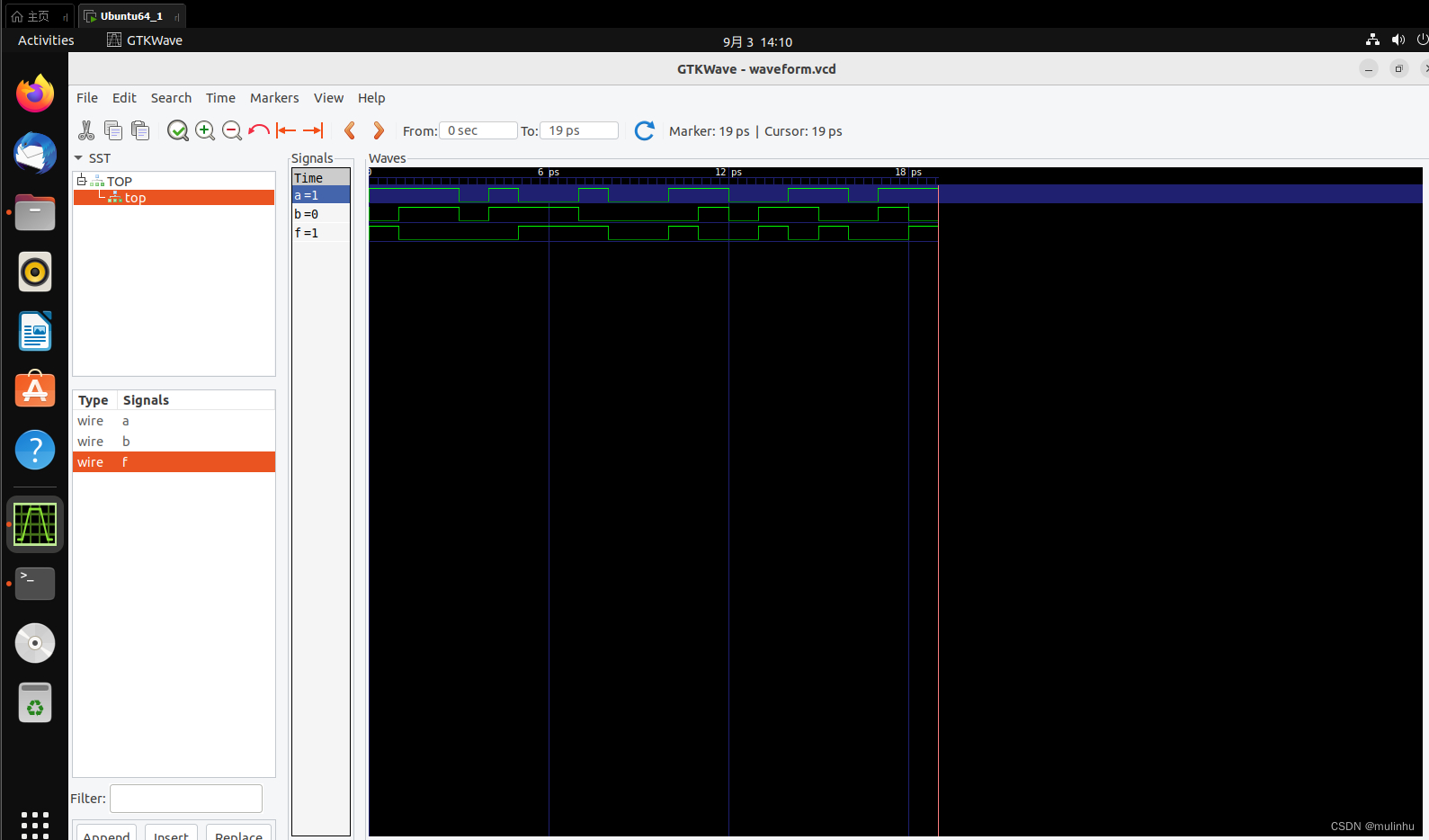

Linux下利用iverilog进行功能仿真,利用gtkwave查看仿真输出波形

原文:《Linux下利用iverilog进行功能仿真》

linux下面进行硬件仿真,可以使用modelsim,但是modelsim不是开源软件,安装需要破解,很是麻烦,而iverilog是linux下的一款开源仿真软件,利用它再配合s…

Circuits--Sequential Logic--Latches and Flip-Flops--Edgedetect

网址:https://hdlbits.01xz.net/wiki/Edgedetect

module top_module (input clk,input [7:0] in,output [7:0] pedge

);reg [7:0] r_in;always

Circuits--Sequential Logic--Shift Refisters--Lfsr5

网址:https://hdlbits.01xz.net/wiki/Lfsr5

module top_module(input clk,input reset, // Active-high synchronous reset to 5h1output [4:0] q

); always(posedge clk)beginif(reset 1b1)q < 5h1;else beginq[4] < 1b0 ^ q[0];q[3] < q[4];q[2] &l…

Circuits--Sequential Logic--Counters--Count clock

网址:https://hdlbits.01xz.net/wiki/Count_clock 自己写:

module top_module(input clk,input reset,input ena,output pm,output [7:0] hh,output [7:0] mm,output [7

HDLBits学习------Problem 106~114

参考链接:HDLBits导学 Problem 106 4-bit shift register 问题:设计一个4bit异步复位,拥有同步置位和使能的右移移位寄存器。

areset : 寄存器复位为0load : 将data[3:0]输入至移位寄存器中ena : 使能信号控制向右移动(q[3]q[2]q…

数字芯片设计中的面积优化方法

前言:数字芯片设计工程师在设计的时候要考虑三个方面,PPA,即Performance、Power和Area。本文讲解在实际项目中,如何对前端面积进行有效优化。

理论方法

本文首先参考书籍《FPGA设计实战演练(高级技巧篇)》…

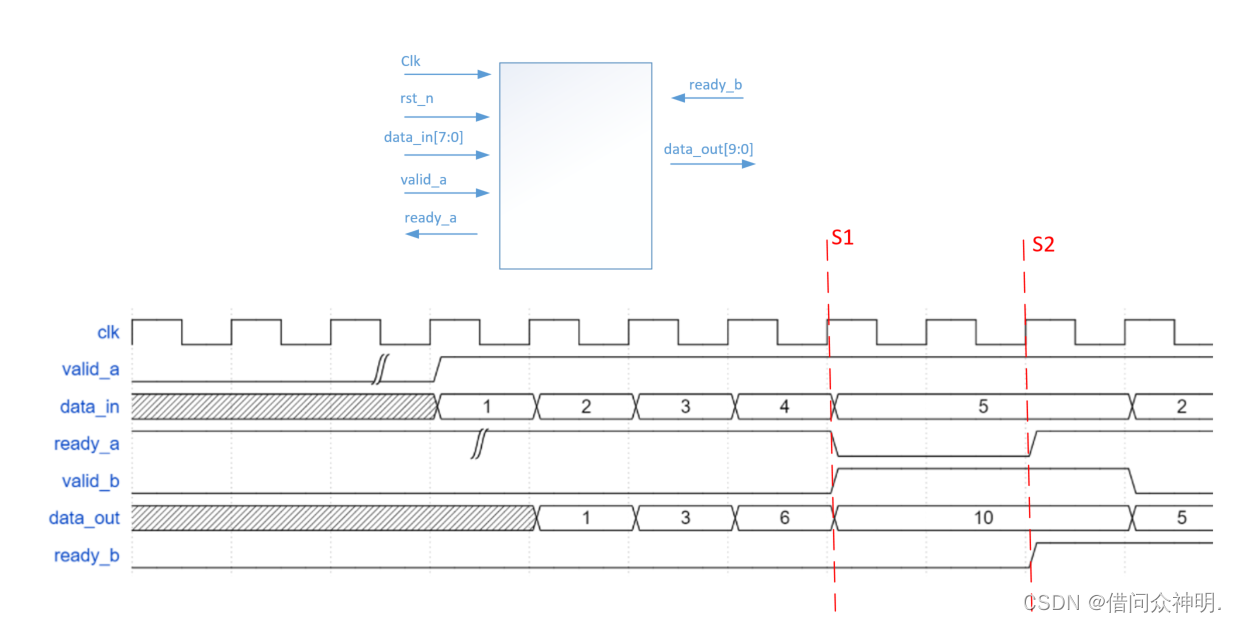

数字芯片设计——握手与反压

前言:在芯片设计或者FPGA设计过程中,流水设计是经常用到的,但是考虑数据安全性,需要与前后级模块进行握手通信,这时候就需要对流水数据进行反压处理,本文将具体介绍握手与反压。 目录 握手协议

握手与反压

反压

不带存储体的反压

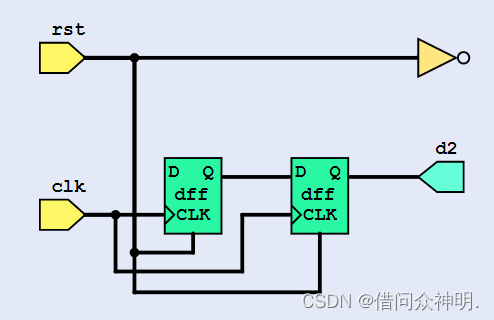

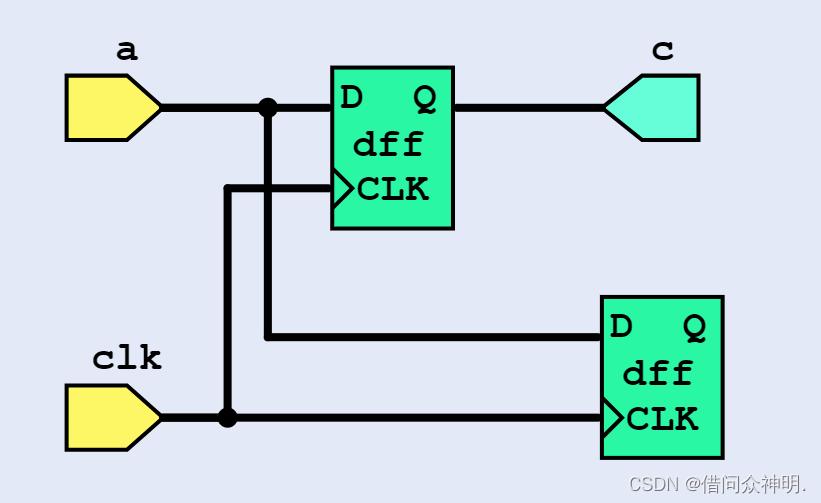

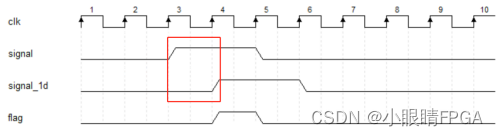

边沿检测—Verilog

在设计中,需要检测某一信号发生0->1跳转的变化时,可以采用边沿检测。 边沿检测的实现思路如下图所示,为了保证采样信号沿的准确,首先对信号进行打拍处理。由波形图可以看出,上升沿出现时,可以由d1与d2非…

波特率分频监测模块理解-基于apb_uart项目

文章目录模块介绍波特率定义主要代码描述代码实例模块介绍

该组件模块只要功能是检测特定波特率下的时钟分频是否正确,主要指IRQ.CLK在寄存器的控制下,是否正确分频成baud_out,其中 DIV2与 DIV2 寄存器的值和各个波形之间的频率关系如下图所…

HDLBits学习------Problem 36~42

参考链接:HDLBits导学 Problem 36: Conditional ternary operator(Conditional) 概述:Verilog跟C语言一样有一个三元运算符( ? : )

condition ? if_true : if_false 问题:给出四个无符号数,请找到其中的最小值。无符号数可以使…

HDLBits学习------Problem 10~18

参考连接:HDLBits导学 Problem 10 : Vectors 概述:什么是 Verilog 中的向量(vector)?向量是一组 wire 信号的集合,通过赋予这一组信号的集合一个名称,以便于访问其中的 wire 信号。

向量类似于…

HDLBits学习------Problem 28~35

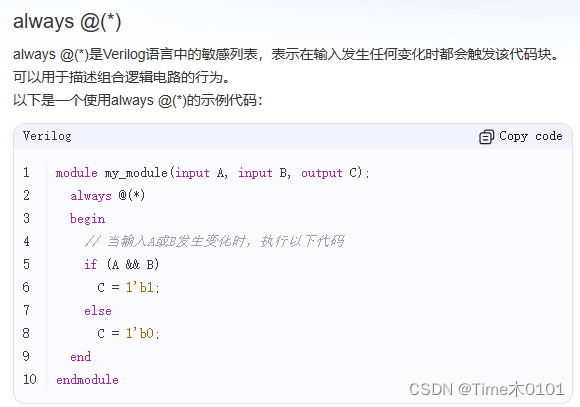

参考链接:HDLBits导学 Problem 28: Always blocks(combinational) (Alwaysblock1) 问题:使用assign语句和组合always块来构建与门 解决:

// synthesis verilog_input_version verilog_2001

module top_module(input a, input b,output wire …

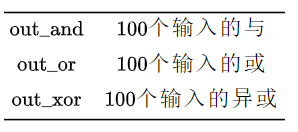

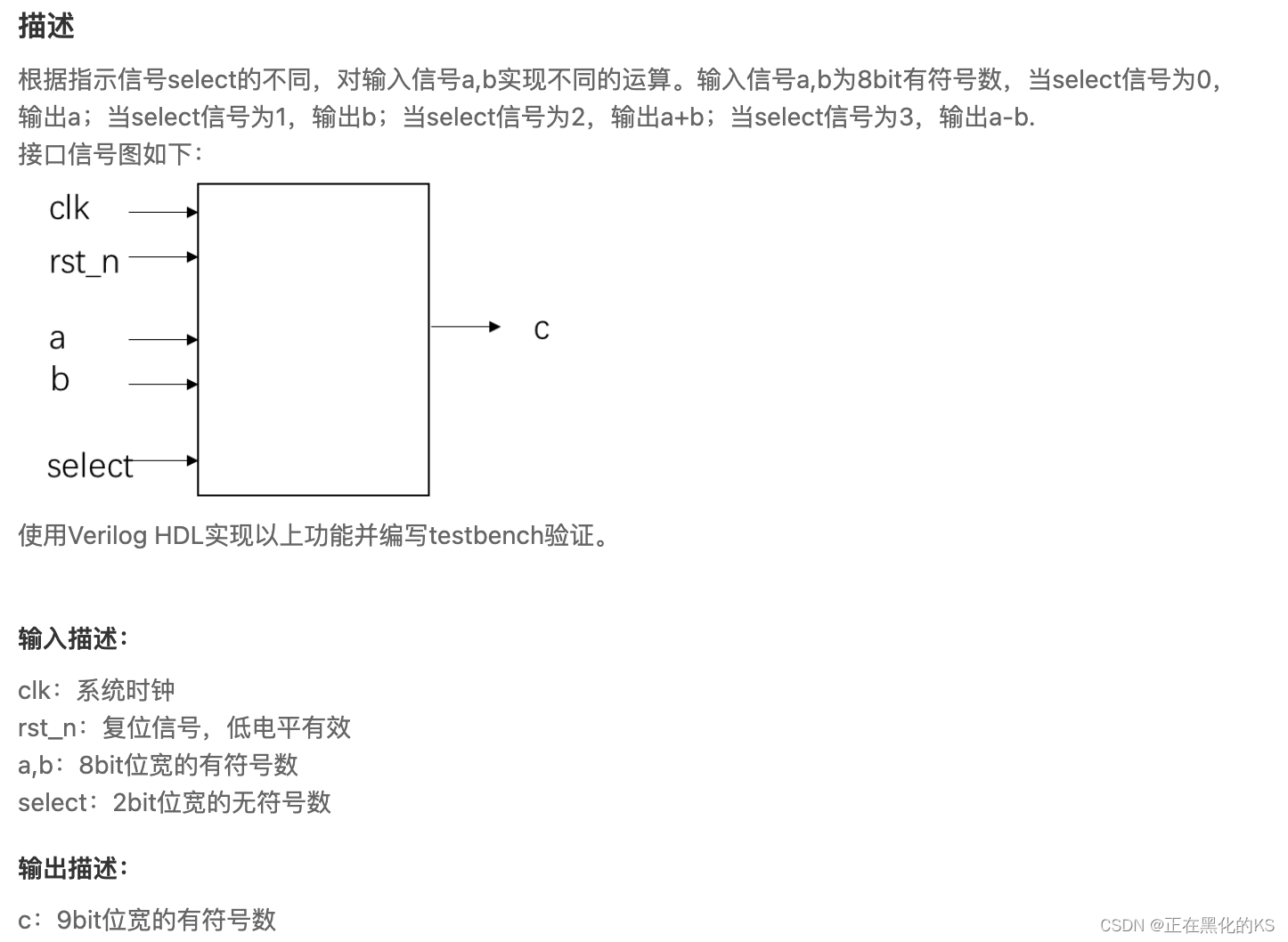

「Verilog学习笔记」多功能数据处理器

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 分析 注意题目要求输入信号为有符号数,另外输出信号可能是输入信号的和,所以需要拓展一位,防止溢出。 timescale 1ns/1ns

module data_…

Verilog RTL 新手代码设计 (边沿捕获器、实例化电路模块并互联、多路选择器、交叉开关、优先编码器)

1.边沿捕获器

举例来说,一个在CLK时钟驱动下,对输入信号IN进行上跳沿捕获的电路,它的Verilog代码如下所示,

module top(CLK , // input clockIN , // input OUT ); // output

input CLK; input IN; outpu…

使用SystemVerilog简化FPGA中的接口

FPGA工程师们应该都会吐槽Verilog的语法,相当的不友好,尤其是对于有很多接口的模块,像AXI4/AXI-Lite这种常用的总线接口,动不动就好几十根线,写起来是相当费劲。当然现在Xilinx推荐使用纯bd文件的方式来设计FPGA&#…

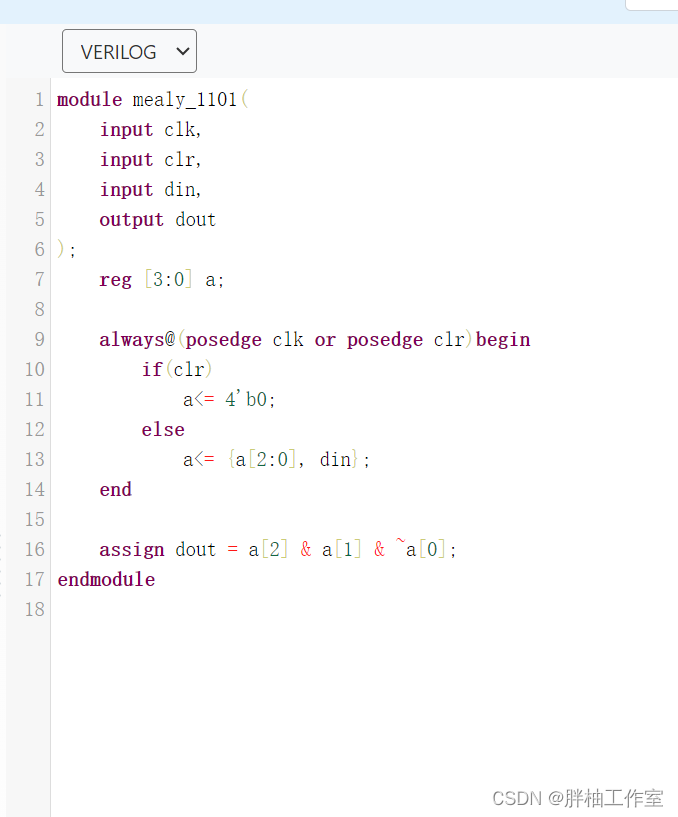

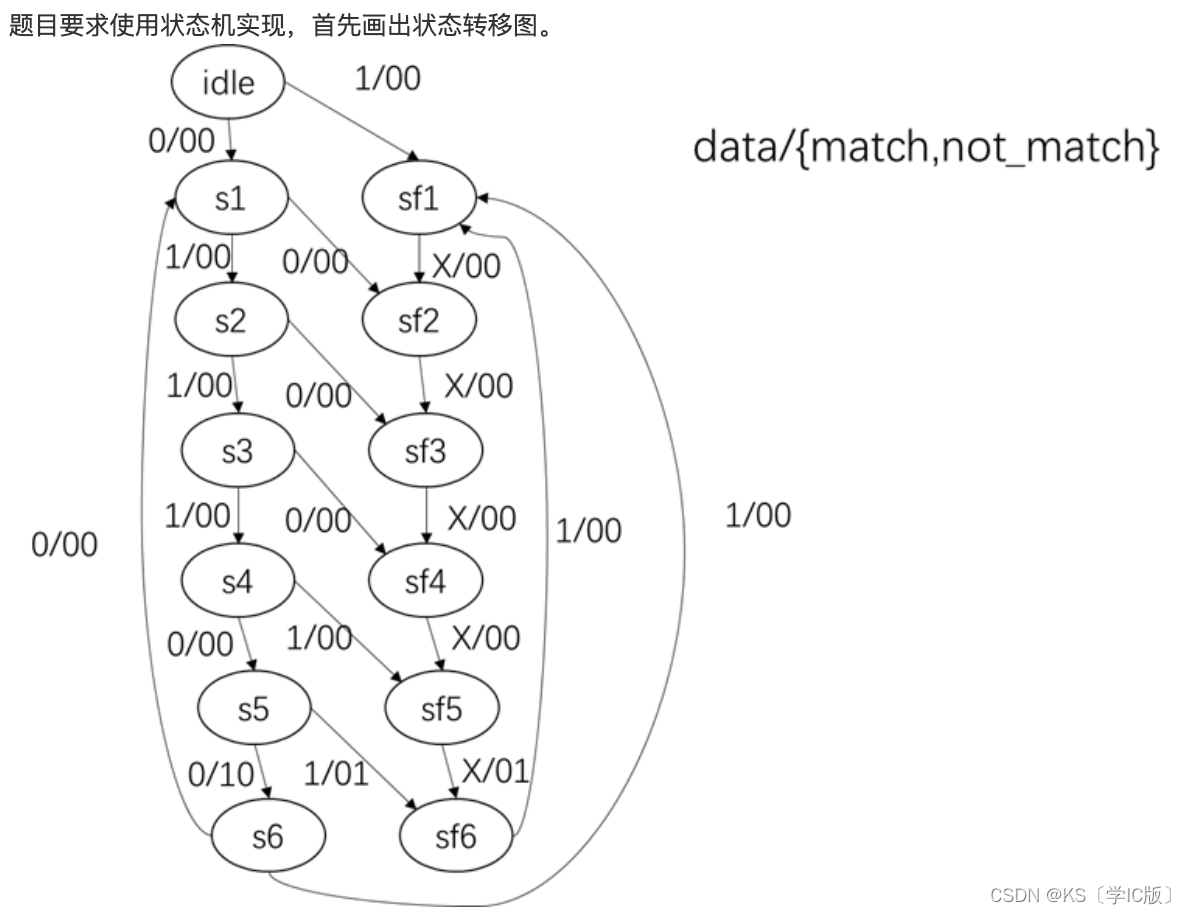

2. 验证1101序列(Mealy)

题目要求: 用 M e a l y \rm Mealy Mealy型状态机验证 1101 1101 1101序列

题目描述: 使用状态机验证 1101 1101 1101序列,注意:允许重复子序列。

方法一: 去掉 M o o r e \rm Moore Moore的 s 4 s_4 s4ÿ…

Verilog刷题[hdlbits] :Module cseladd

题目:Module cseladd

One drawback of the ripple carry adder (See previous exercise) is that the delay for an adder to compute the carry out (from the carry-in, in the worst case) is fairly slow, and the second-stage adder cannot begin computing …

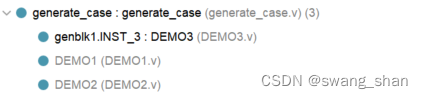

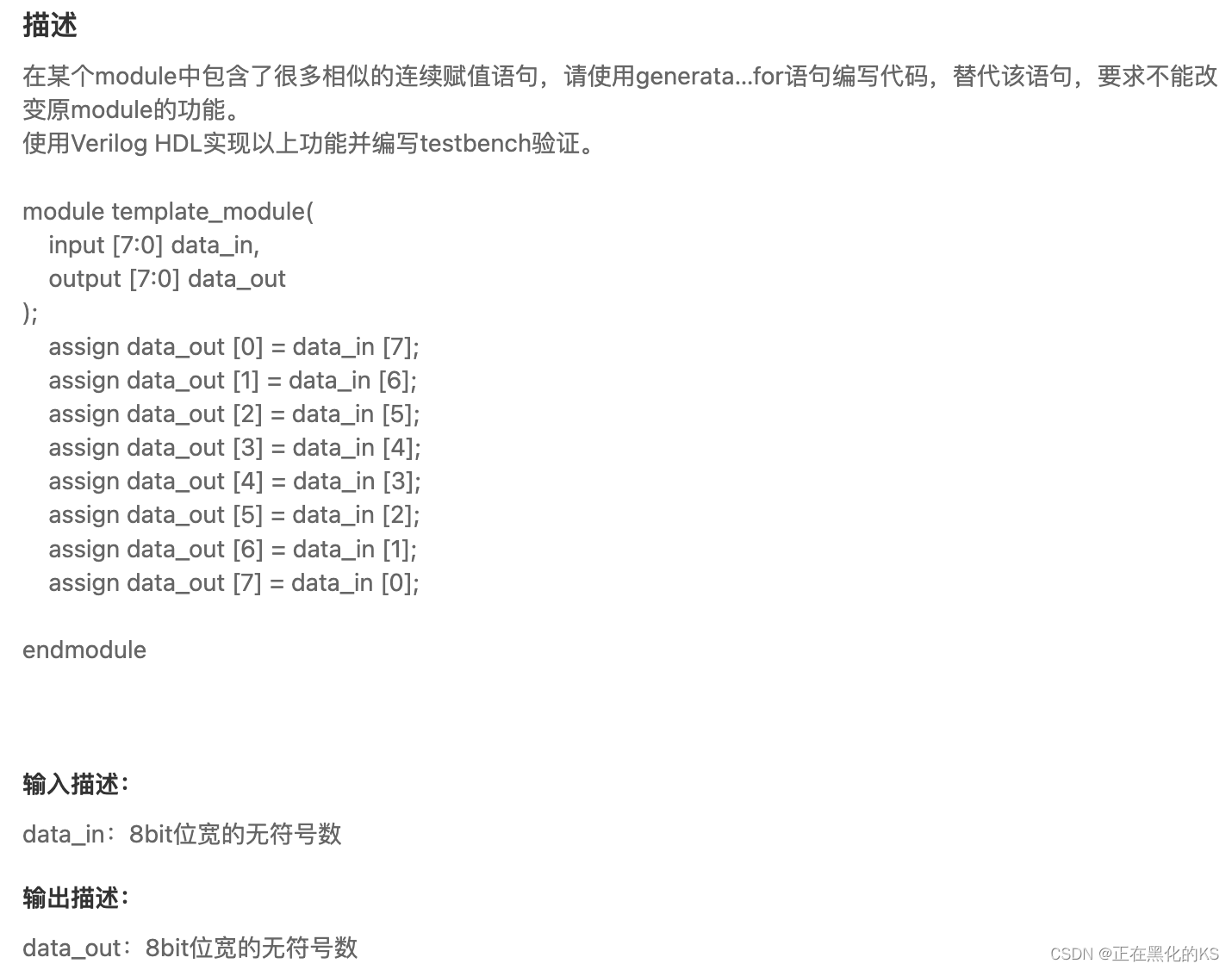

Verilog系列:generate常用用法

Verilog中generate语句允许在解析阶段(Elaboration-time)对某些语句进行选取或者重复。

这些语句可以包括模块实例引用的语句、连续赋值语句、always语句、initial语句和门级实例引用语句等。解析阶段是指仿真开始前的一个阶段,此时所有的设…

什么样的人适合从事IC Design的工作?

今天不聊技术,聊点别的。

从事一项工作,能力是两方面的。一方面是技术,技术上的事情,有些人先天就适合干这个。有些人不管什么开发平台什么语言什么工具,15 分钟完全上手。还有人有很好的engineering sense࿰…

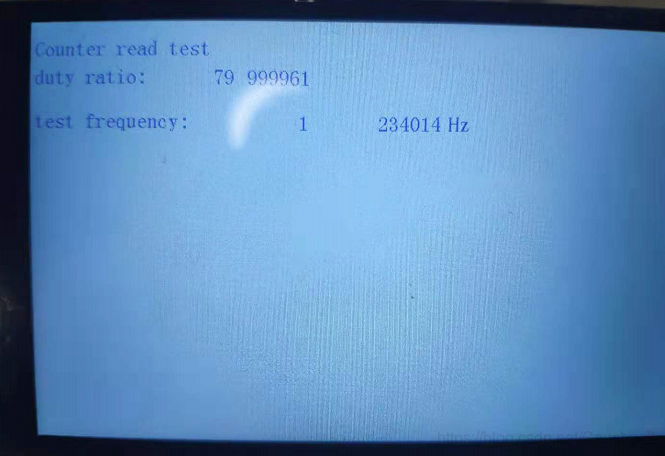

基于FPGA+stm32的的等精度频率计

整体功能:实现正弦波(方波)的频率和周期测量,并测量方波信号占空比

测量方法:

1.频率测量:使用等精度测量方法:等精度测量,由于设置的门控时间是5000个待测的信号的周期࿰…

HDLBits学习------Problem 1~9

参考连接:HDLBits导学

Problem 1 : Zero 问题:没有输入,输出0 解决:

module top_module(output zero

);// Module body starts after semicolonassign zero 0;

endmodule Problem 2 : Wire 问题:使用wire让输出等于…

HDLBits学习------Problem 115~117

参考链接:HDLBits导学 Problem 115 Rule90 问题:Rule90 是一道根据一些有趣的规则来生成一维序列的题目。

规则很简单。一维序列中元素有 1,0 两种状态,分别对应开,关状态。

在每个时钟边沿到来时刻,元素的下一个状态…

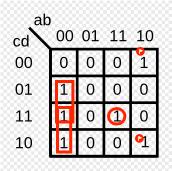

HDLBits学习------Problem 72~79

参考链接:HDLBits导学 Problem 72 3-variable 问题:根据卡诺题来实现电路: 思路:使用卡洛图得到表达式 第一个方框中,只有b的值保持不变且为1,所以这个框化简出来是b

第二个方框中,只有c的值都…

I2S接口以及Verilog实现数据接收

I2S(Inter—IC Sound)总线,是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线专门用于音频设备之间的音频数据传输。I2S总线有三条数据信号线: (1)BCLK:串行时钟,也叫位时钟,对应…

FPGA实现 NIC 10G 网卡,纯verilog代码编写,提供工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的UDP方案3、10G网卡基本性能简介4、详细设计方案接口概述PCIe HIPDMA IFAXI总线接口时钟同步处理TXQ和RXQ队列TXCQ和RXCQ队列完成EQ MAC PHY流水线队列管理发送调度程序端口和接口数据路径以及发送和接收引擎分段内存接口 5、vivado工程详…

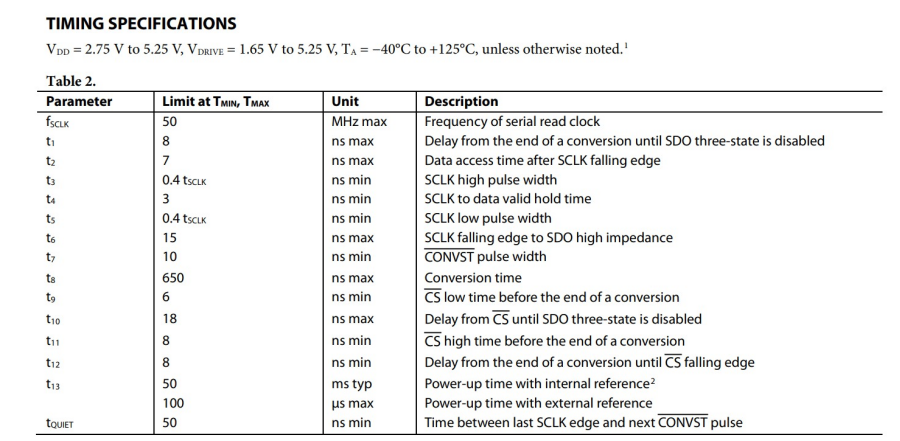

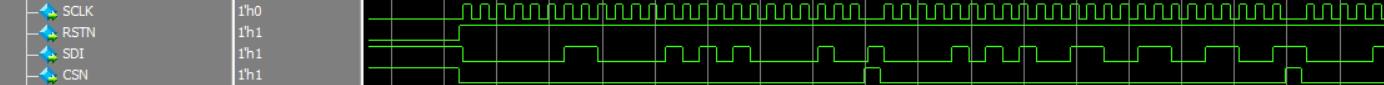

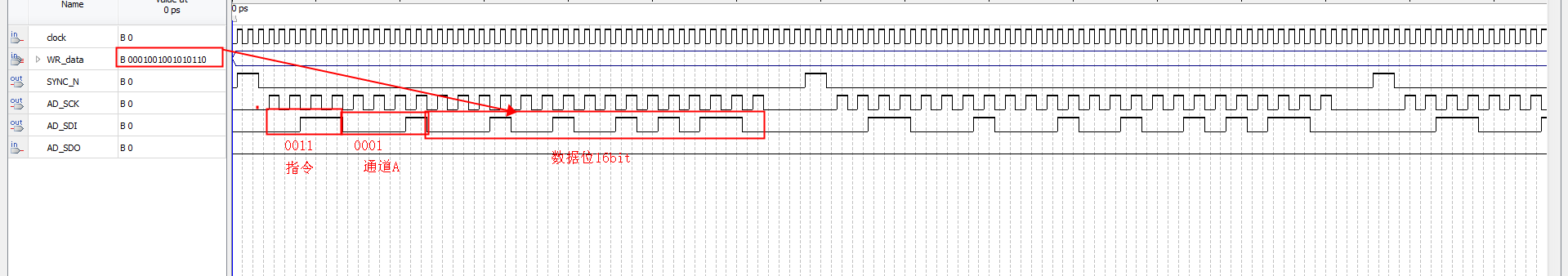

SPI接口的FPGA实现(二)——配置DAC

这一篇主要结合DAC81416的datasheet来进一步阐述如何配置DAC。先附上DAC81416的datasheet的链接。

一、datasheet概述

如果自己不做电路板,DAC81416的datasheet需要关注的方面并不多。该DAC一共16个输出通道,可以通过一系列的配置其内部寄存器的操作输…

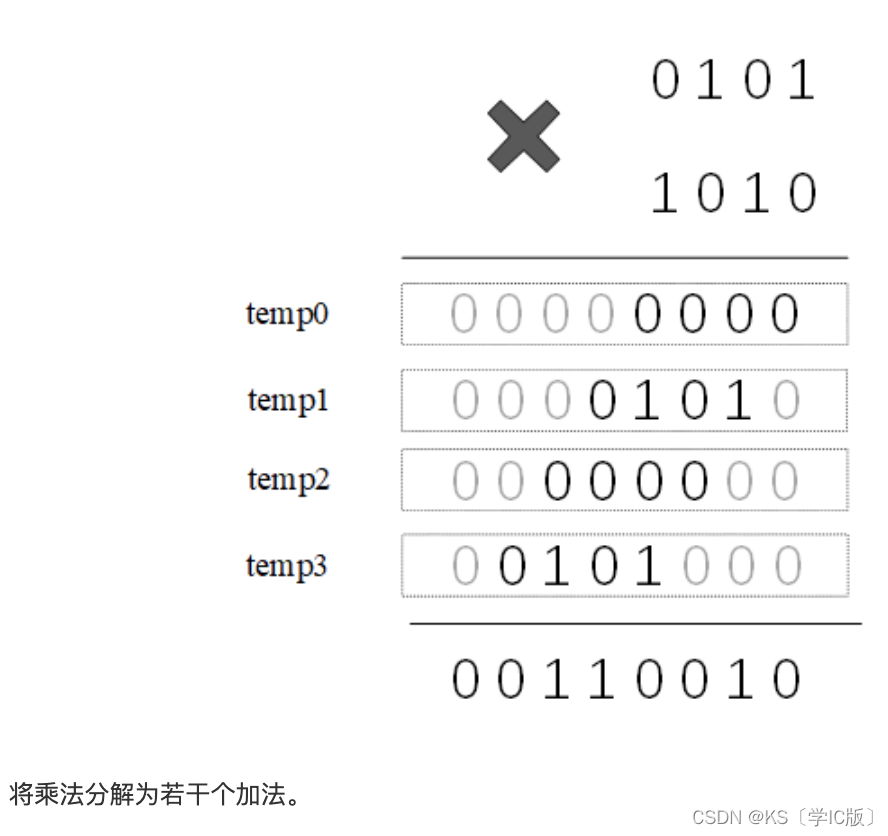

「Verilog学习笔记」编写乘法器求解算法表达式

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 timescale 1ns/1nsmodule calculation(input clk,input rst_n,input [3:0] a,input [3:0] b,output [8:0] c);reg [8:0] data1, data2 ; assign c data2 ; always (posed…

建立(Setup Time)和保持时间(Hold Time)

建立Setup Time和保持时间Hold Time建立时间(Setup Time)保持时间(Hold Time)建立时间(Setup Time)

所谓建立时间指的是数据在时钟沿到来前需要保持的最短时间。

保持时间(Hold Time)

保持时间(Hold Time)是指时钟沿之后数据需要保持不变的最短时间。

Fsm onehot

module top_module(input in,input [9:0] state,output [9:0] next_state,output out1,output out2);assign out1(state[8]|state[9])?1:0;assign out2(state[9]|state[7])?1:0;assign next_state[0](state[0]&(~in)) |(state[1]&(~in)) |(state[2]&(~in)) |(sta…

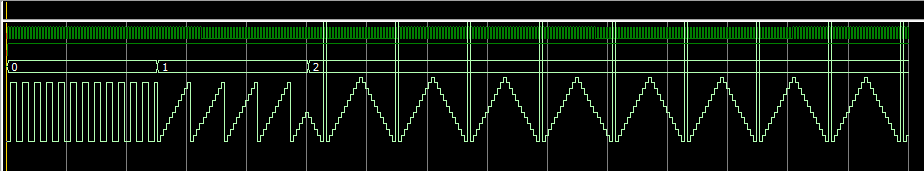

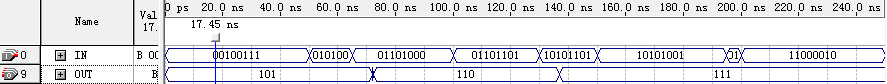

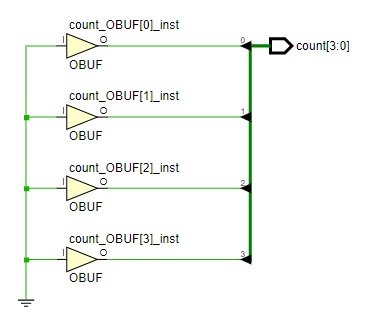

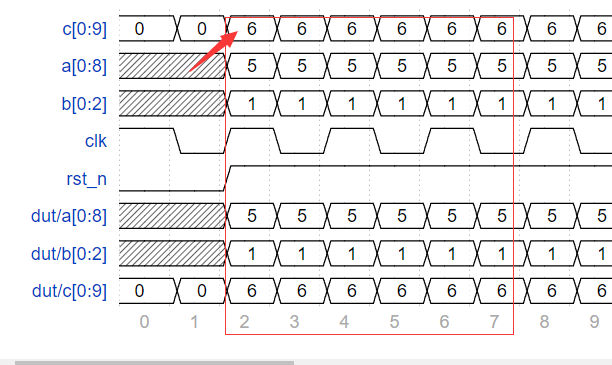

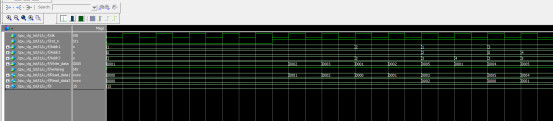

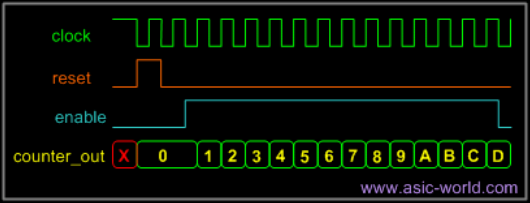

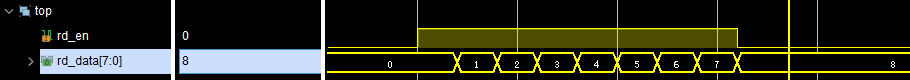

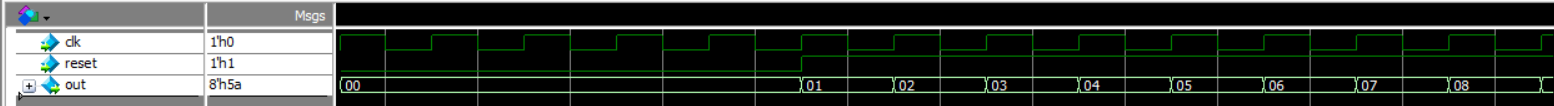

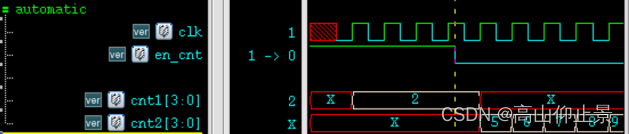

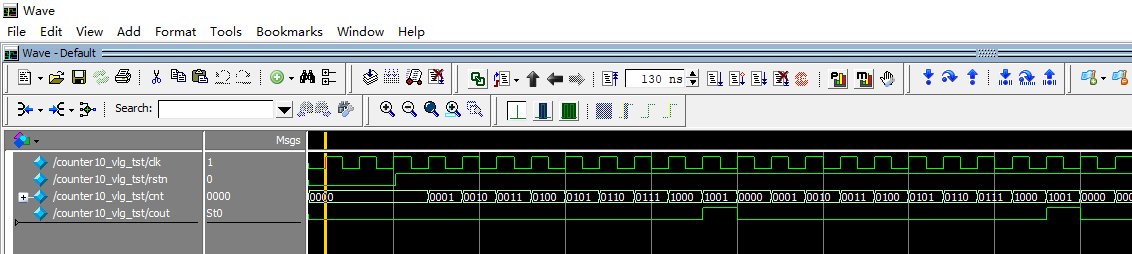

【verilog-10位计数器, vcs仿真和问题记录】

前言

此文介绍了十位计数器的verilog代码编写以及使用vcs的仿真流程。

10位计数器

具体代码如下 timescale 1ns/1psmodule tb();reg clk;reg rstn;wire [3:0]cnt;counter dut(.clk(clk), .rst(rstn),.cnt(cnt));initial beginclk < 0;forever begin#5 clk < !clk;ende…

Vivado2018.1约束文件中使用#报错记录

在使用vivado做两位十进制数倒计时动态显示时,出现以下错误。

提示错误:

[DRC NSTD-1] Unspecified I/O Standard: 4 out of 34 logical ports use I/O standard (IOSTANDARD) value DEFAULT, instead of a user assigned specific value. This may ca…

HDLBits学习------Problem 80~97

参考链接:HDLBits导学 Problem 80 : D flip-flop (Dff) 问题:实现一个D触发器 解决:

module top_module (input clk, // Clocks are used in sequential circuitsinput d,output reg q );//// Use a clocked always block// copy d to …

HDLBits学习------Problem 98~105

参考链接:HDLBits导学 Problem 98 Four-bit binary counter 问题:设计一个4bit的计数器,从0~15,共16个周期。reset是同步复位且复位为0 解决:

module top_module (input clk,input reset, // Synchro…

FPGA驱动OLED Verilog代码 (一)------ SPI写模块

一、概述: 我本身没有很仔细的去学习SPI的时序,而是参照了之前STM32驱动OLED时模拟的时序来写的,其中写一个字节的时序如下

/*************************************************************************/

/*函数功能: 通过SPIO软件模拟SPI…

FPGA驱动OLED Verilog代码 (四)------ 字符和汉字显示

一、概述: 首先展示一下成果图,使用RAM的读写来完成,下面依次介绍各个模块 二、OLED显示原理(部分) oled分为7页,每一页有128个字节用来显示 首先先设置页地址,然后设置列的低地址和高地址&…

关于FPGA如何快速生成模块的例化模板(实用)

关于FPGA如何快速生成模块的例化模板(实用) 语言 :Verilg HDL 、VHDL EDA工具:ISE、Vivado、Quartus II 关于FPGA如何快速生成模块的例化模板(实用)一、引言二、快速生成例化模块的几种方法1. IP核的例化模…

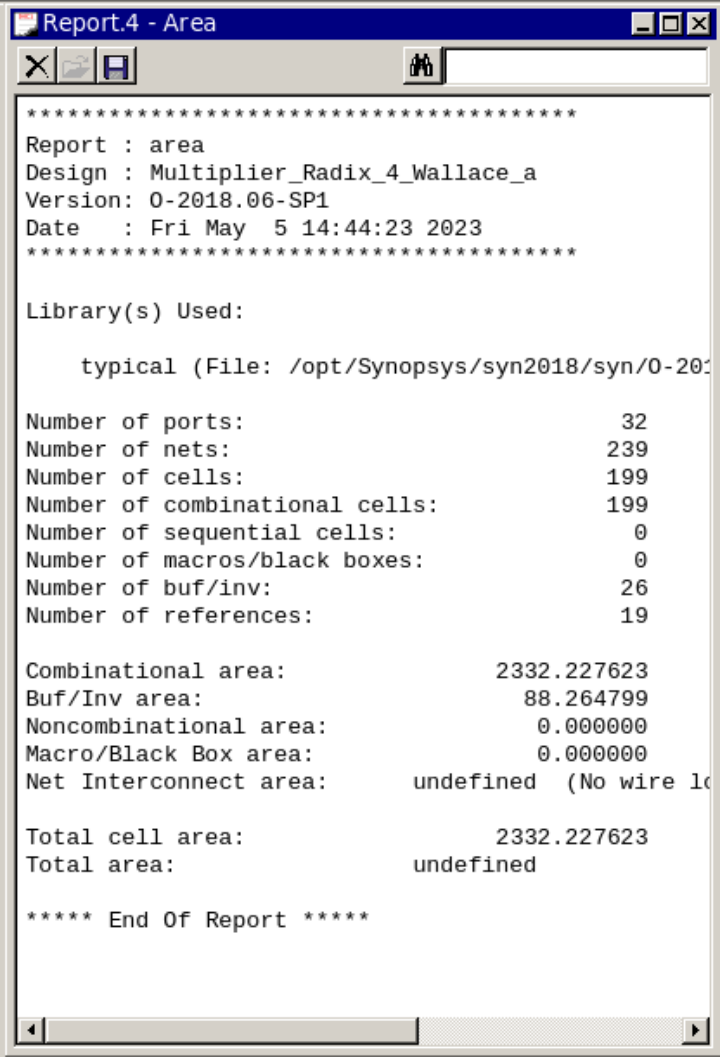

[Verilog语言入门教程] 乘法器(顺序 Booth 并行 Wallace) 原理与实现

依公知及经验整理,原创保护,禁止转载。 专栏 《Verilog》 <<<< 返回总目录 <<<<

乘法器可以分为以下几种类型:

顺序乘法器(Sequential Multiplier):顺序乘法器是最简单的乘法器类型,采用逐位相乘的方法实现。这种乘法器适用于小规模的乘法运算…

Modelsim添加中间变量

参考链接:Modelsim查看中间变量 原文我自己感觉不怎么好理解,所以自己又总结了一下) 编译好编写的仿真文件后,点击需要仿真的文件开始仿真 点击后界面如图 看到Objects界面只有我们在仿真文件中定义的变量(也就是例化…

FPGA驱动OLED Verilog代码 (五)------ 动态显示字符

一、概述 前面已经介绍了向RAM中写入静态字模数据来显示静态的字符和汉字。接下来实现动态显示字符在OLED屏的不同位置。 动态显示字符的核心就是从ROM中读取字符的字模,但取出来的字模数据如果直接写进RAM的话,只能实现字符在某一页的显示,而…

FPGA驱动LCD1602(IIC) Verilog代码(三)------ LCD初始化

一、概述: 前面已经完成了lcd写数据/命令,那么lcd的初始化就比较简单了,就是先发送命令复位设置lcd,然后发送数据过去交给lcd显示就好了。 lcd的显示比较简单一点,只需要传输要显示字符的ascll码,lcd就会显…

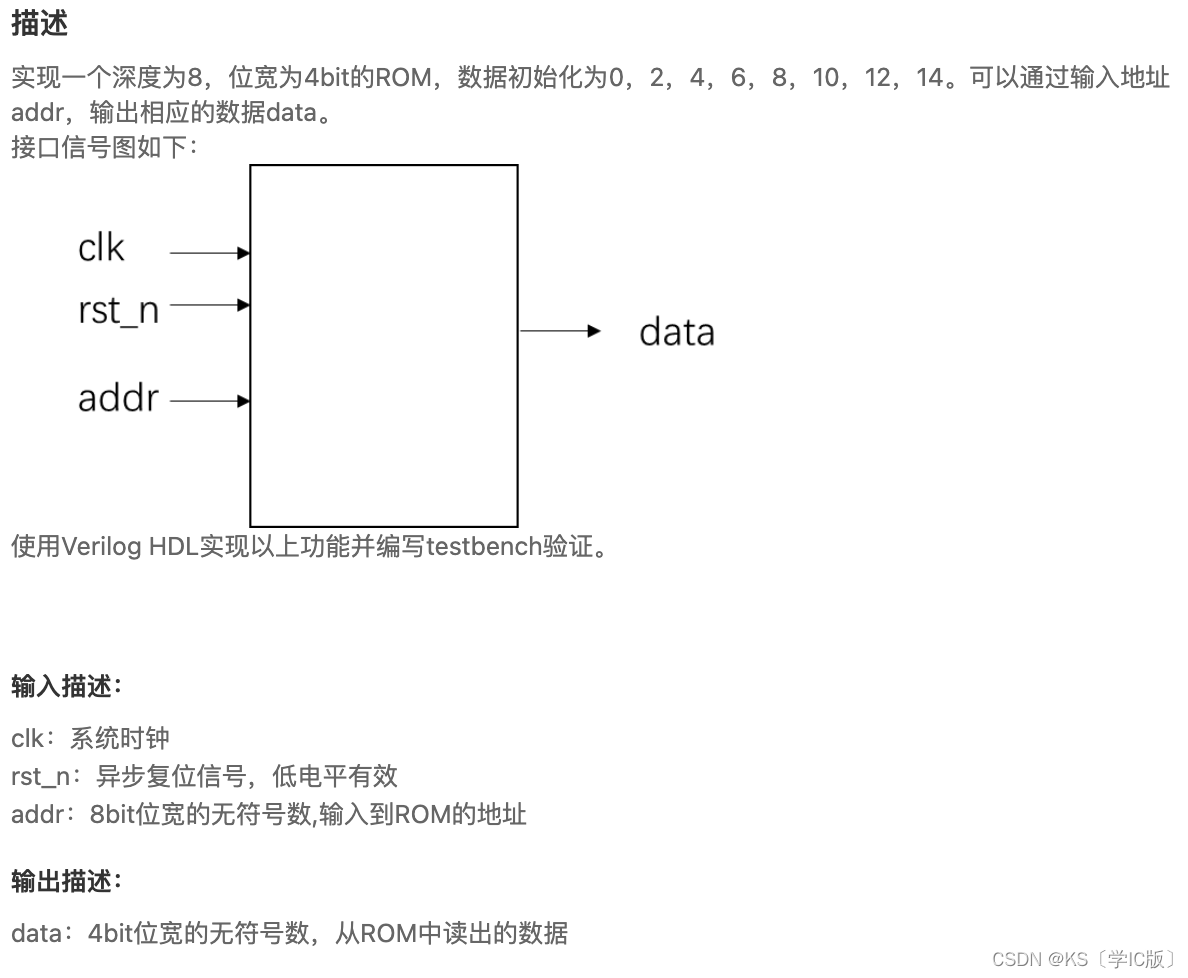

「Verilog学习笔记」ROM的简单实现

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 分析 要实现ROM,首先要声明数据的存储空间,例如:[3:0] rom [7:0];变量名称rom之前的[3:0]表示每个数据具有多少位࿰…

【Verilog 教程】4.6 Verilog 多路分支语句

关键词:case,选择器 case 语句是一种多路条件分支的形式,可以解决 if 语句中有多个条件选项时使用不方便的问题。

case 语句 case 语句格式如下:

case(case_expr)condition1 : true_statement1 ;condition2 …

「Verilog学习笔记」异步复位的串联T触发器

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 分析 这道题目里我们有两个需要明确的点: 1. 什么是异步复位 2. 什么是串联的T触发器 关于第一个点,可以看我的这篇文章,已经整理好了&a…

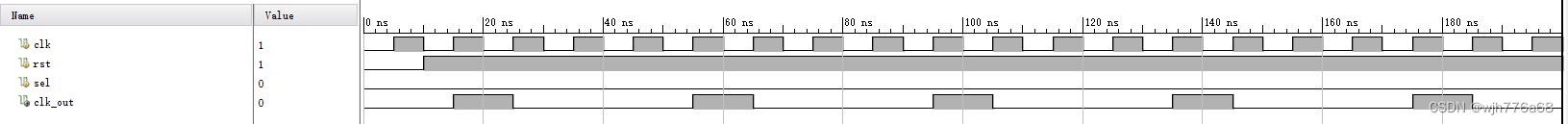

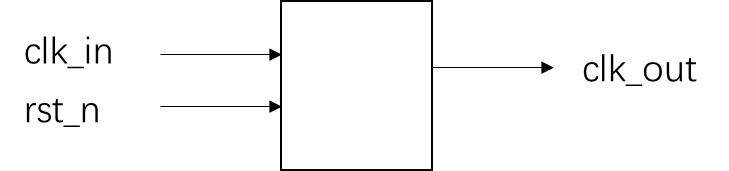

【HISI IC萌新虚拟项目】Package Process Unit模块整体方案·PART3

5. 模块方案说明

5.1CRG 模块方案说明

5.1.1简介

CRG 模块实现复位信号的滤抖功能,可滤除小于100ns的低电平复位毛刺,并对复位信号进行同步化处理。同时,对100MHz的输入时钟信号进行2分频,作为 CPU_IF模块和TEST_CORE模块的工作时钟。

5.1.2接口信号 信号位宽I/O描述

Verilog Tutorial(10)如何实现可复用的Verilog设计?

本文将讨论可以用来实现代码可复用性的参数parameter和generate语句(生成语句)。与大多数编程语言一样,设计者也应该尽量使verilog代码尽可能地具备可复用性----这能够减少未来项目的开发时间,因为设计者可以更轻松地将代码从一个…

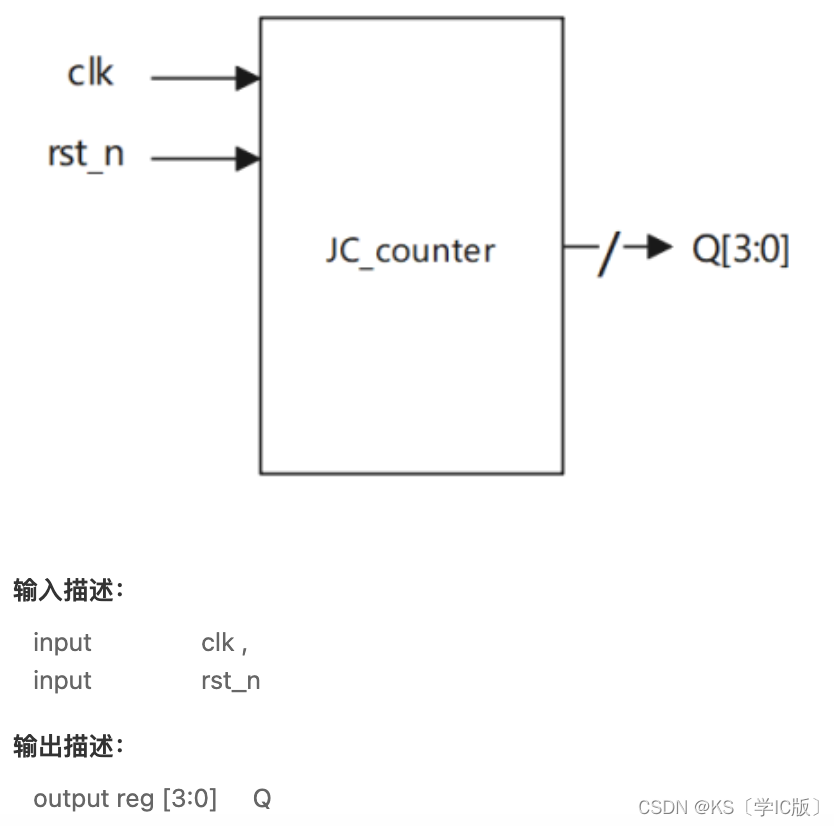

「Verilog学习笔记」 Johnson Counter

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 timescale 1ns/1nsmodule JC_counter(input clk ,input rst_n,output reg [3:0] Q

);always (posedge clk or negedge rst_n) begin…

「Verilog学习笔记」自动贩售机1

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 自动贩售机中可能存在的几种金额:0,0.5,1,1.5,2,2.5,3。然后直接将其作为状态机的几种状…

《Clock Domain Crossing》 翻译与理解(3)寄存器处理输出端口

前言:本系列将对sunburst design网站的2008最佳文章《Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog》进行翻译和基于自我理解的分析阐述,本文主要介绍寄存器输出端口在跨时钟域时的处理。

发射时钟域的信号同…

基于FPGA的电风扇控制器verilog,视频/代码

名称:基于FPGA的电风扇控制器verilog

软件:QuartusII

语言:Verilog

代码功能:

基于FPGA的电风扇控制器 运用 EDA SOPO实验开发系统设计一个基于FPGA的电风扇定时开关控制器,能实现手动和自动模式之间的切换。要求:

(1)KI为电…

在FPGA板上用Verilog实现车牌识别

一个车牌识别系统先在Matlab中实现,然后将其在FPGA Xilinx Spartan-6上使用Verilog实现。以下是FPGA上系统的测试环境。 图像存储器: 存储10个图像并将其转换为.dat格式(gray data)。我们使用$ readmemh(可复合&#…

使用Verilog HDL在FPGA上进行图像处理

该FPGA项目旨在详细说明如何使用Verilog处理图像,读取Verilog中的输入位图图像(.bmp),处理并将处理结果用Verilog写入输出位图图像。提供了用于读取图像,图像处理和写入图像的完整Verilog代码 。

在这个FPGA Verilog项…

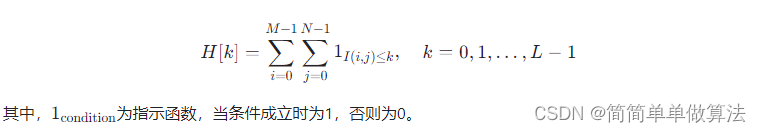

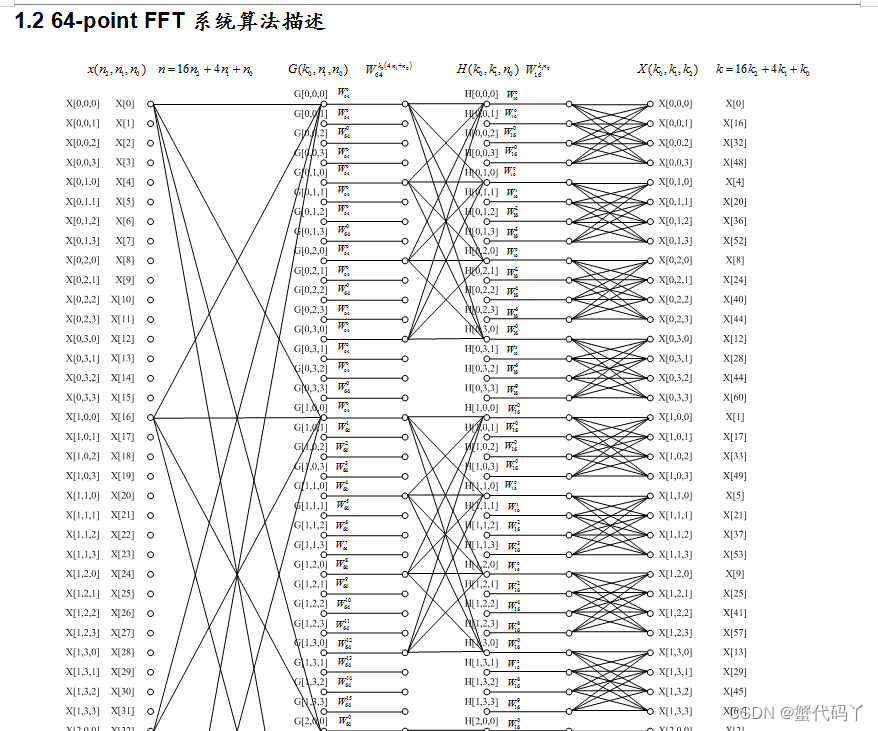

雷达信道化接收算法及论证(持续更新)

信道化接收 在中频输入端采用信道化方式,即按频率划分若干信道,相当于将一个宽带接收机分解成若干个窄带接收机,可以使其具备窄带接收机的特性,具有更高的灵敏度及动态范围,下面对信道化接收进行理论推导。 数字信道化…

verilog 时刻卡死,$time 不递增解决方案

#verilog #问题记录 #已解决

verilog 时刻卡死,$time 不递增解决方案

先说结论, 在写testbench 时,需要注意在一些 always 中加上延时,避免某个 always 不间断的一直仿真运行,导致仿真时刻卡住,时刻不递增…

用verilog实现数字频率计

数字频率计

此设计是我在东南大学大三短学期数字系统课程设计的课题。(如果有学弟学妹看到这篇文章,希望可以给你们提供一定的帮助,但也希望别直接controlc,controlv)

同时,本文中的代码因为经过再编辑&…

【verilog中的阻塞赋值与非阻塞赋值】

文章目录1: 非阻塞赋值语句2:阻塞赋值语句总结1: 非阻塞赋值语句

非阻塞(Non_Blocking)赋值方式块结束后才完成赋值操作。b的值并不是立刻就改变的。对于时序电路中的always块的reg信号,一般采用非阻塞语句赋值。这种方式的赋值并不是马上执行的&#x…

HDLbits-Circuits(电路)-Sequential Logic(顺序逻辑)

Latiches and Flip-Flops(锁存器与触发器)

1. Dff

A D flip-flop is a circuit that stores a bit and is updated periodically, at the (usually) positive edge of a clock signal. D flip-flops are created by the logic synthesizer when a cloc…

分频电路-verilog

1. 2分频

module div_2(clk,rst,out);

input clk,rst;

output out;reg q;

always(posedge clk or negedge rst)if(!rst)q<1b0;elseq<~q;

assign outq;

endmodule

2. 偶数分频

module div_8 (clk,rst,out);input clk,rst;

output out;

reg out;

reg [2:0]cnt;always(po…

verilog描述一个一百进制计数器(两位数码管显示)

FPGA可以实现多种多样的时序电路,用Verilog语言可以描述任意进制的计数器。本文描述了一个一百进制的计数器,由两个十进制计数器级联而成。每个十进制计数器可以送显至一位数码管。

资源链接:

https://download.csdn.net/download/benchusp…

「Verilog学习笔记」流水线乘法器

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 timescale 1ns/1nsmodule multi_pipe#(parameter size 4

)(input clk , input rst_n ,input [size-1:0] mul_a ,input [size-1:0] mul_b ,output …

Verilog Language--Modules:Hierarchy--Module addsub

网址:https://hdlbits.01xz.net/wiki/Module_addsub module top_module(input [31:0] a,input [31:0] b,input sub,output [31:0] sum

)

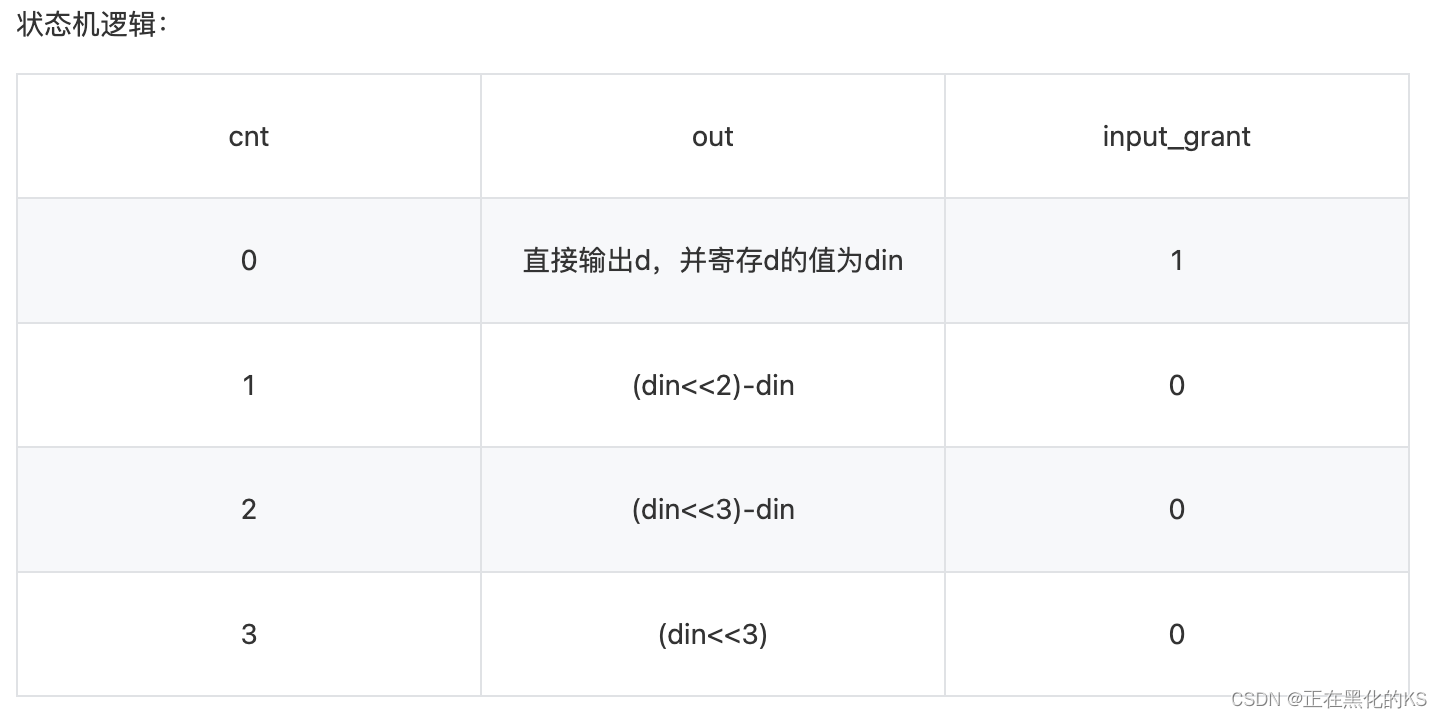

【手撕代码-序列检测1011001-每次输入2bit】

文章目录题目要求:代码实现:状态图:题目要求:

请实现对(1011001)2的序列检测功能,模块每拍并行输入2bit,且顺序为高位先输入,当检测到序列,输出一拍高电平脉…

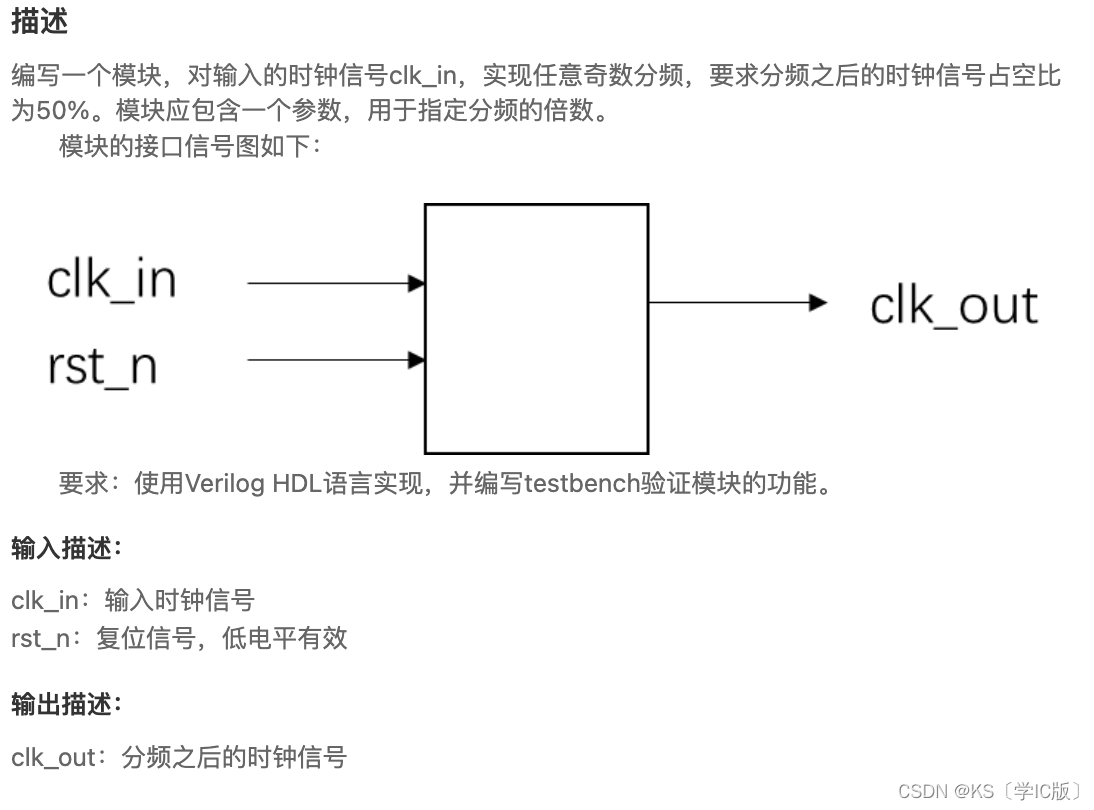

「Verilog学习笔记」任意奇数倍时钟分频

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 timescale 1ns/1nsmodule clk_divider#(parameter dividor 5)

( input clk_in,input rst_n,output clk_out

);parameter CNT_WIDTH $clog2(dividor - 1) ; reg flag1, f…

Verilog Language--More Verilog Features--Adder100i

网址:https://hdlbits.01xz.net/wiki/Adder100i

module top_module( input [99:0] a, b,input cin,output [99:0] cout,output [99:0] sum

fork join_none易错点

本篇博客记录一下自己在实际过程中遇见的易错的语法细节。 两种不同条件下的fork join_none的使用: 1、

program fork_pra;initial beginfor(int i 0; i < 3; i) beginfork $write(i);join_none#0;endendendprogram上述这种,可以看见延时语句在fork…

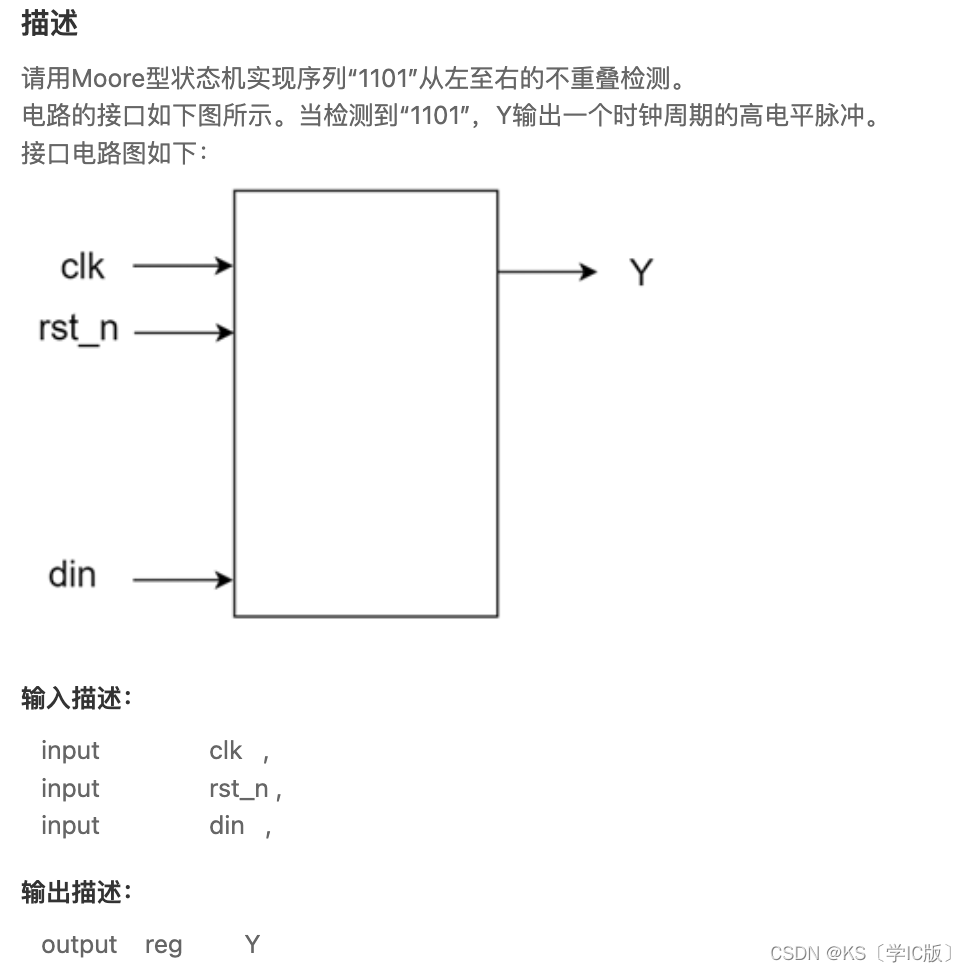

1、验证1101序列(Moore)

题目要求: 用Moore型状态机验证1101序列。

题目描述: 用使用状态机验证1101序列,注意:允许重复子序列。如图 端口描述:

module moore_1101(input clk,//时钟信号input clr,//reset复位信号,高电平有效in…

【Verilog教程】3.2 Verilog 时延

关键词:时延, 惯性时延 连续赋值延时语句中的延时,用于控制任意操作数发生变化到语句左端赋予新值之间的时间延时。

时延一般是不可综合的。

寄存器的时延也是可以控制的,这部分在时序控制里加以说明。

连续赋值时延一般可分为…

Circuits--Combinational Logic--Arithmetic Circuits--Bcdadd4

网址:https://hdlbits.01xz.net/wiki/Bcdadd4

module top_module( input [15:0] a, b,input cin,output cout,output [15:0] sum );wire cout1;wire cout2;wire co

HDLBits:在线学习 Verilog (二 · Problem 10-14)

本系列内容来自于知乎大V:ljgibbs,个人主页为:https://www.zhihu.com/people/ljgibbs,欢迎关注。本系列文章将和读者一起巡礼数字逻辑在线学习网站 HDLBits 的教程与习题,并附上解答和一些作者个人的理解,相…

Circuits--Sequential Logic--Finite State Machines--Fsm3

网址:https://hdlbits.01xz.net/wiki/Fsm3

module top_module(input clk,input in,input areset,output out); //// State transition logic// State flip-flops with asynchronous reset// Output logicparameter A=0, B=1, C=

Circuits--Sequential Logic--Latches and Flip-Flops--Edgecapture

网址:https://hdlbits.01xz.net/wiki/Edgecapture

module top_module (input clk,input reset,input [31:0] in,output [31:0] out

);reg [31:0] r_in;always(posedge clk)beginr_in in;endalways(posedge clk)beginif(reset)beginout < 32d0;endelse beginout…

【Verilog】期末复习——简要说明仿真时阻塞赋值和非阻塞赋值的区别。always语句和initial语句的关键区别是什么?能否相互嵌套?

系列文章

数值(整数,实数,字符串)与数据类型(wire、reg、mem、parameter) 运算符 数据流建模 行为级建模 结构化建模 组合电路的设计和时序电路的设计 有限状态机的定义和分类 期末复习——数字逻辑电路分…

「Verilog学习笔记」非整数倍数据位宽转换24to128

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 要实现24bit数据至128bit数据的位宽转换,必须要用寄存器将先到达的数据进行缓存。24bit数据至128bit数据,相当于5个输入数据第6个输入数据的拼接成一…

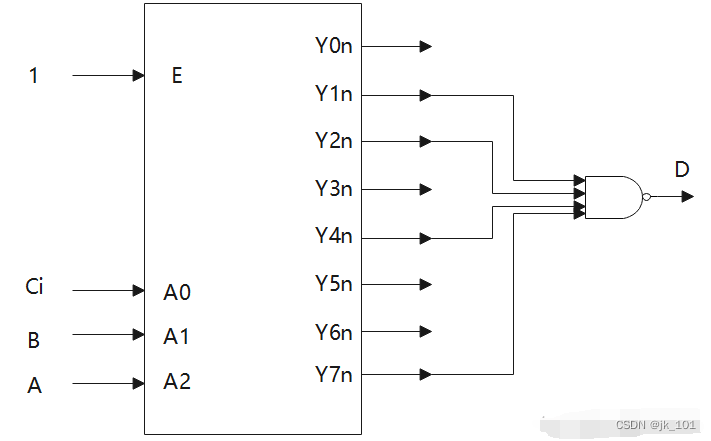

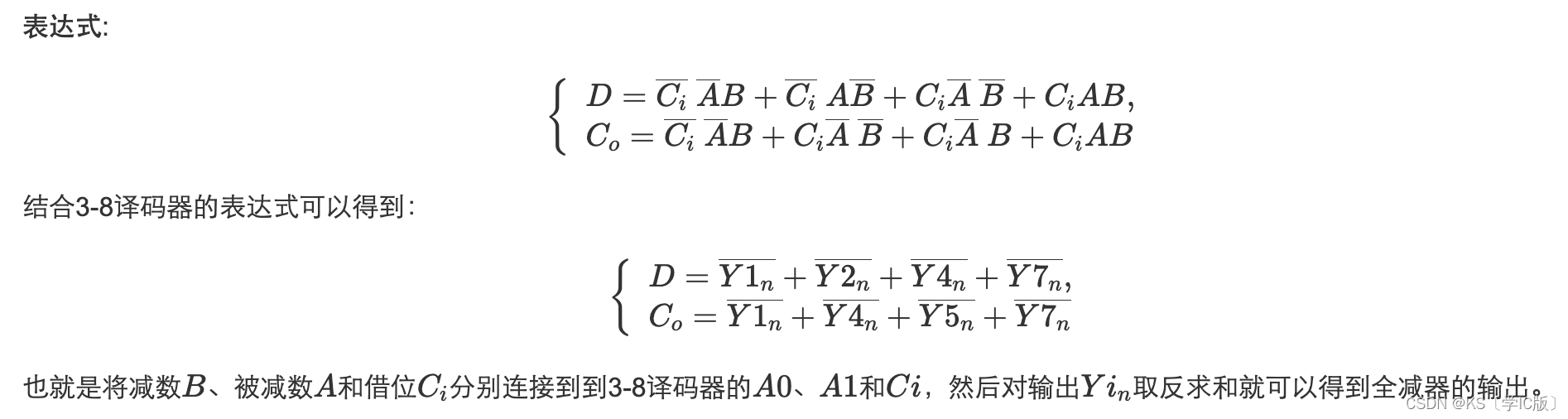

「Verilog学习笔记」使用3-8译码器①实现逻辑函数

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 timescale 1ns/1nsmodule decoder_38(input E1_n ,input E2_n ,input E3 ,input A0 ,input A1…

Vivado导入浮点数据

1、MATLAB生成double类型数据,并导出到文件中。 signal randn(1000,1); writematrix(sinwave,‘signal.dat’,‘Delimiter’,’ ‘); 2、Vivado导入浮点数据 DataSource_Inputfopen("signal.txt","r");while(fopen("signal.txt",&qu…

「HDLBits题解」Wire4

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码 以提供参考 各位可同时参考我的代码和官方题解代码 或许会有所收益 题目链接:Wire4 - HDLBits

module top_module( input a,b,c,output w,x,y,z );assign {w, x, y, z} {a, b, b, c} ;

endmodule

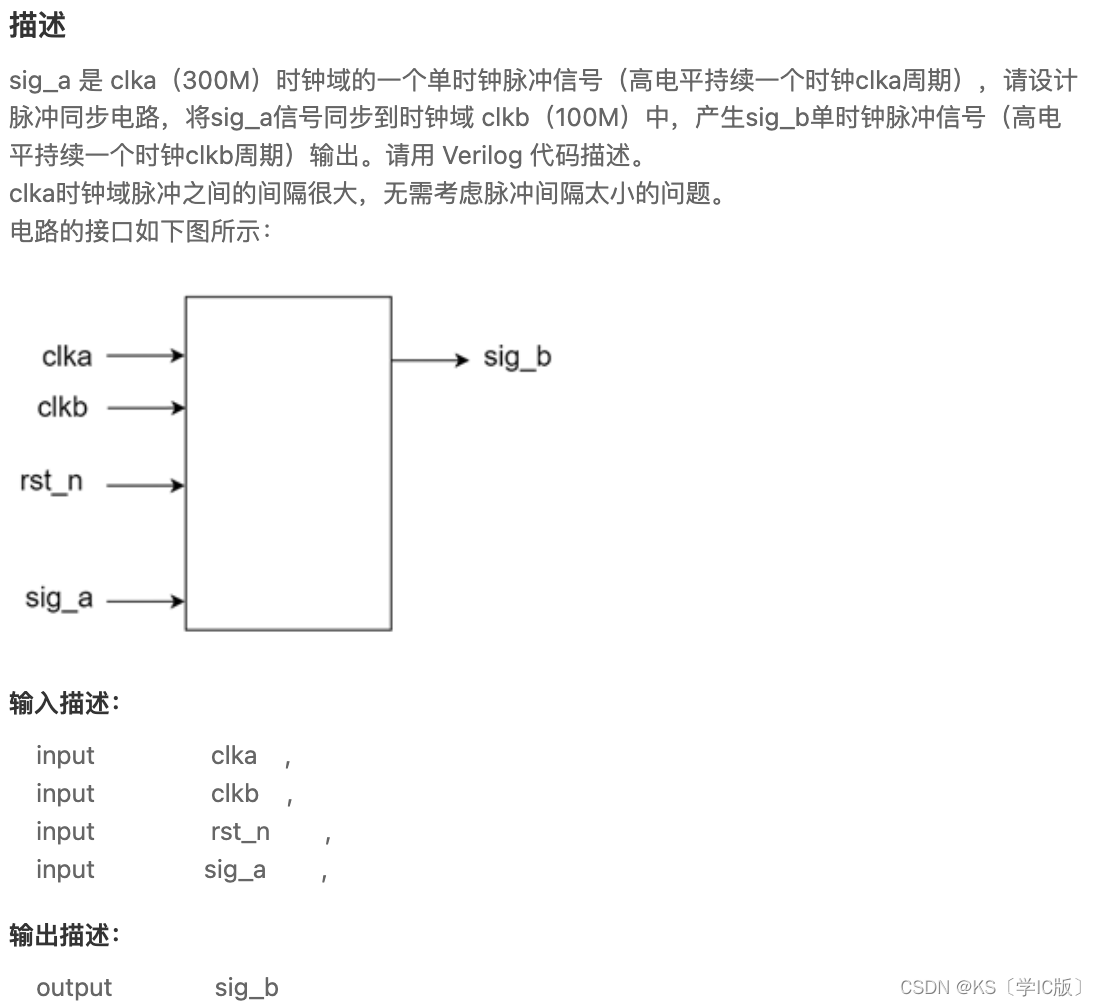

「Verilog学习笔记」 脉冲同步器(快到慢)

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 timescale 100ps/100psmodule pulse_detect(input clka , input clkb , input rst_n ,input sig_a ,output sig_b

);reg Q_sig_a ; reg Q_buff0, …

HDLBits:Dualedge双边沿触发

verilog无法实现双边沿触发只能单边沿触发,所以我们要实现双边沿触发的方法如下: reg temp,temp1;always (posedge clk) begintemp < d ^ temp1;endalways (negedge clk) begintemp1 < d ^ temp;endassign q temp ^ temp1;原理如下:

…

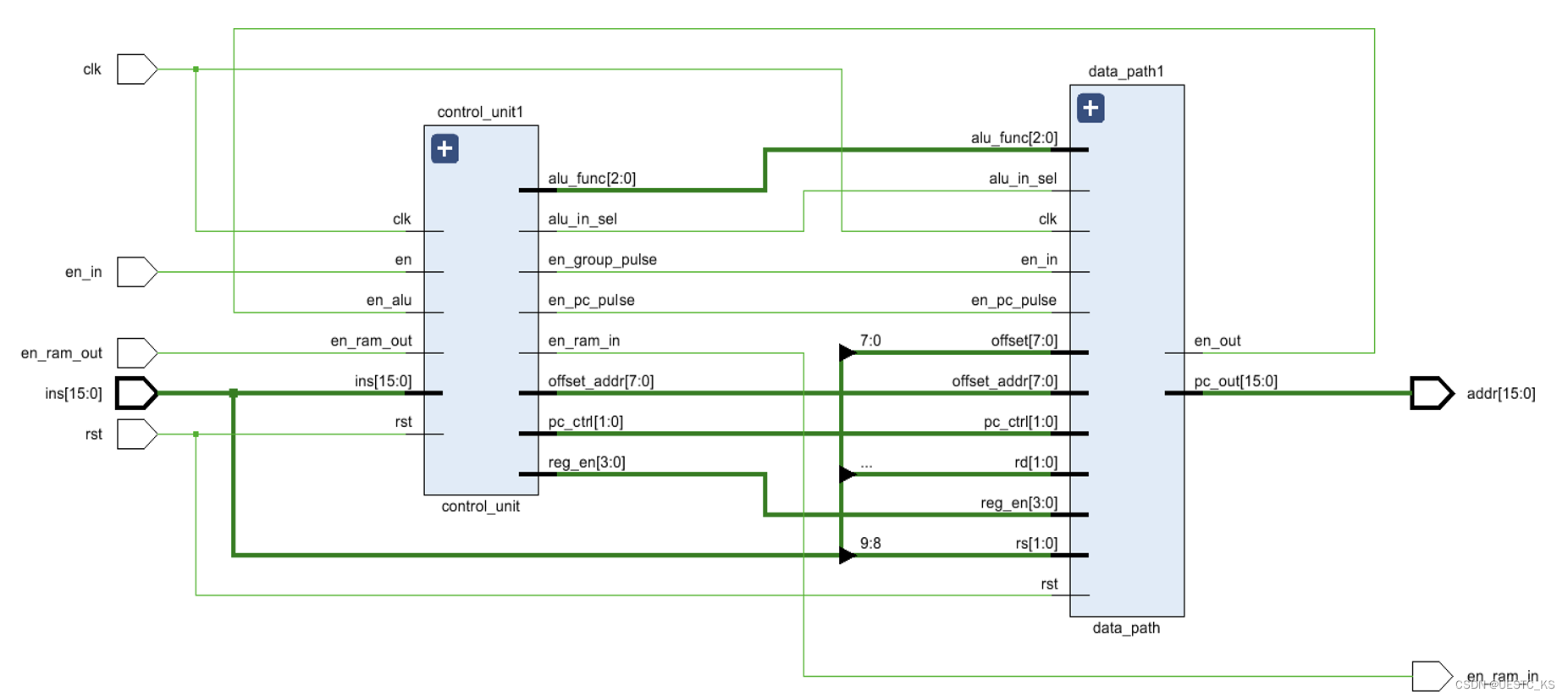

【quartus13.1/Verilog】swjtu西南交大:计组课程设计

实验目的:

通过学习简单的指令系统及其各指令的操作流程,用 Verilog HDL 语言实 现简单的处理器模块,并通过调用存储器模块,将处理器模块和存储器模块连接形成简 化的计算机核心部件组成的系统。 二. 实验内容 1. 底层用 Verilog…

音乐播放器蜂鸣器ROM存储歌曲verilog,代码/视频

名称:音乐播放器蜂鸣器ROM存储歌曲

软件:Quartus

语言:Verilog

代码功能: 设计音乐播放器,要求至少包含2首歌曲,使用按键切换歌曲,使用开发板的蜂鸣器播放音乐,使用Quartus内的RO…

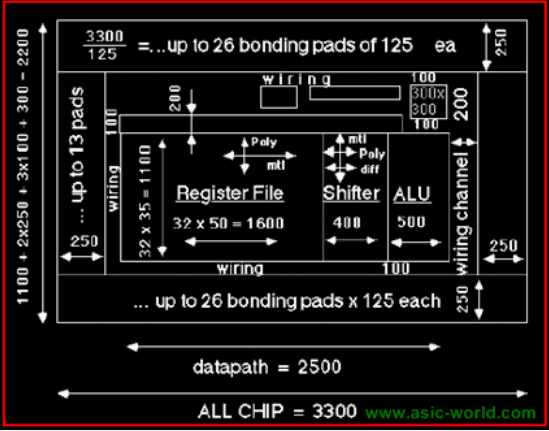

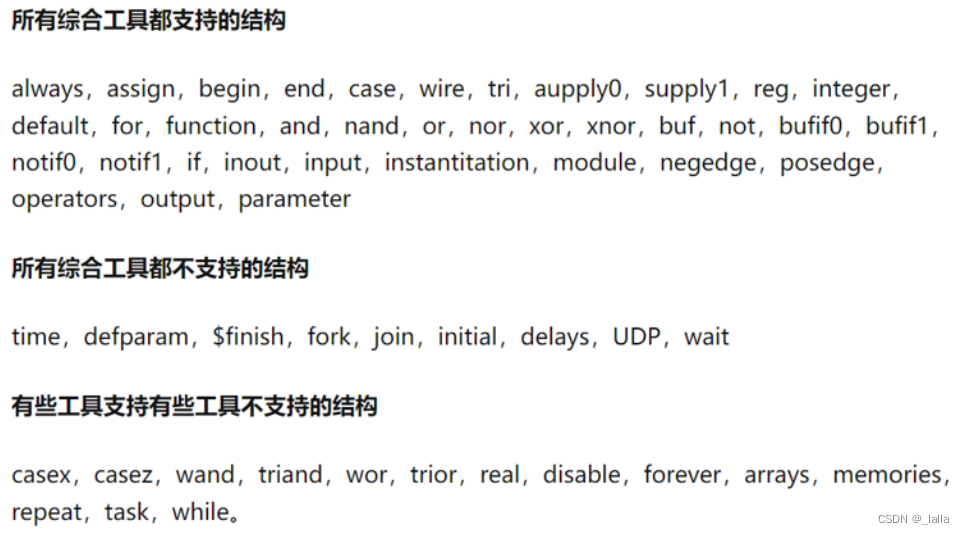

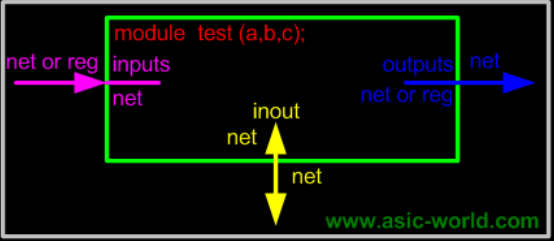

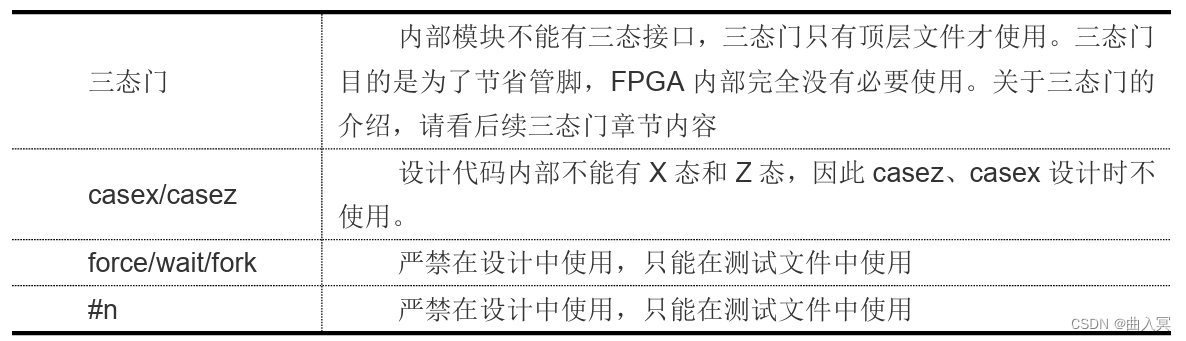

ASIC-WORLD Verilog(16)综合

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----Asic-World网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加点自己的理解)分享给大家。 这是网站原文&…

「HDLBits题解」Counters

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码 以提供参考 各位可同时参考我的代码和官方题解代码 或许会有所收益 题目链接:Count15 - HDLBits

module top_module (input clk,input reset, // Synchronous active-high resetoutput [3:0] q

); always…

「Verilog学习笔记」信号发生器

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 方波的实现,较为简单,只需要设置一个计数器,使输出保持10个时钟为0,跳变为20,再保持10个时钟。依次循环。可以按…

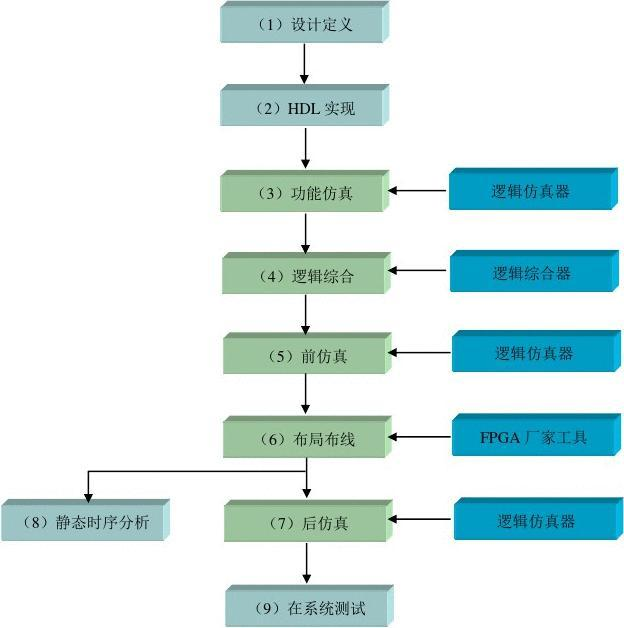

ASIC-WORLD Verilog(2)FPGA的设计流程

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文&…

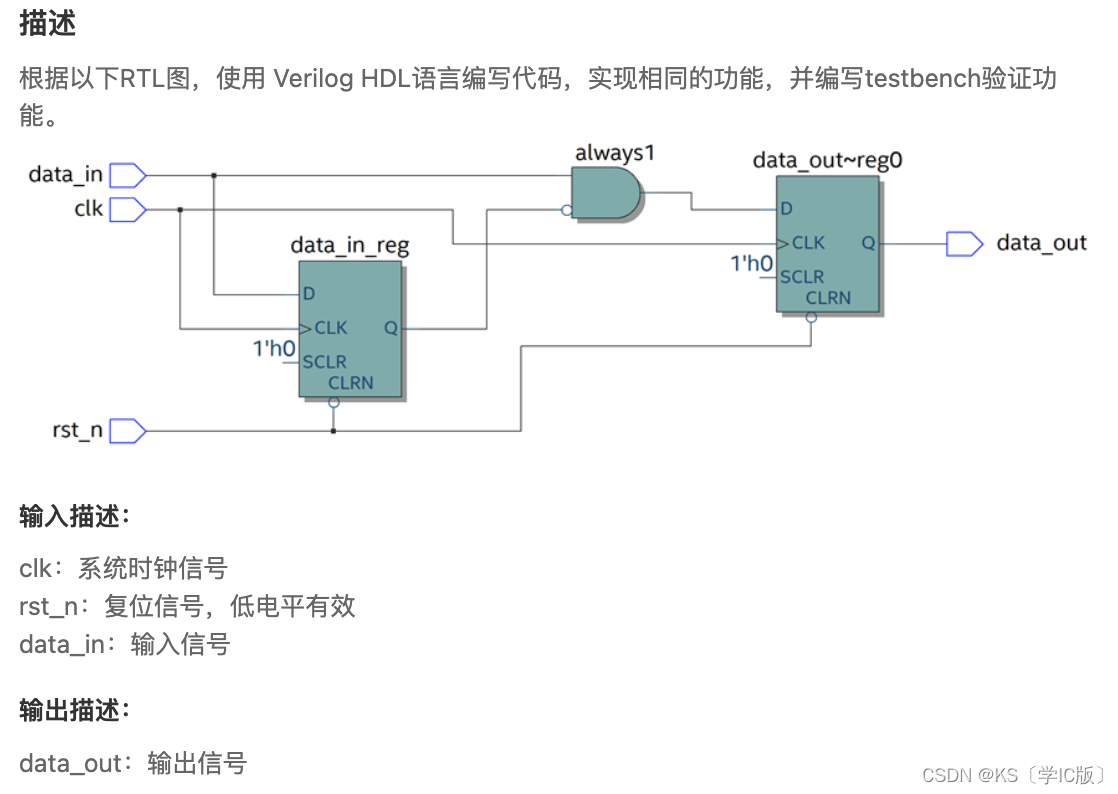

「Verilog学习笔记」根据RTL图编写Verilog程序

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 观察题目给出的RTL图,主要的器件是两个D触发器,一个与门。D触发器含有异步复位信号,且为低电平有效。data_in输入到D触发器,…

SystemVerilog基础:并行块fork-join、join_any、join_none(二)

相关阅读

SystemVerilog基础https://blog.csdn.net/weixin_45791458/category_12517449.html 在第一节中,我们讨论了并行块中的fork-join块和fork-join_any块,了解了它们的差异,本文将继续讨论fork-join_none块的使用。 fork-join_none并行块…

「Verilog学习笔记」数据串转并电路

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 关于什么是Valid/Ready握手机制: 深入 AXI4 总线(一)握手机制 - 知乎 时序图含有的信息较多,观察时序图需要注意:…

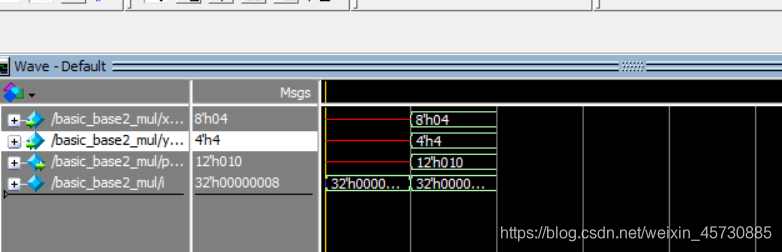

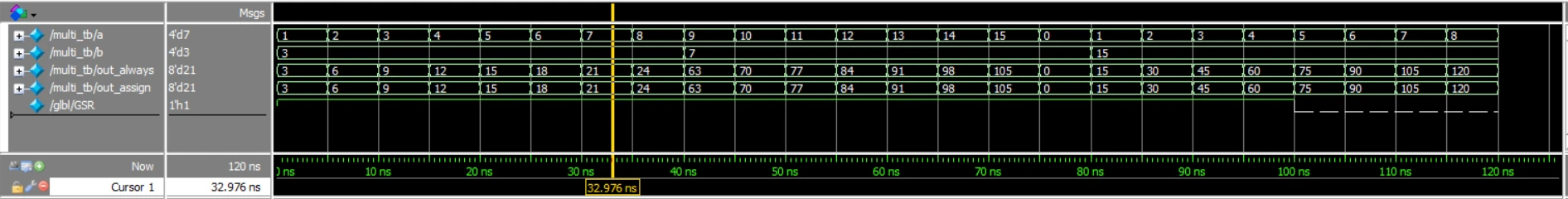

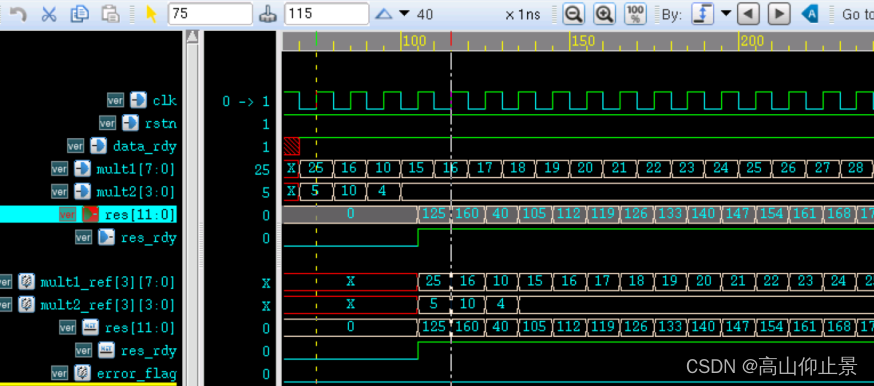

QuartusII和Modelsim联合仿真实现不带时钟信号的简单乘法器

创建项目 找个地方新建文件夹,设置这个项目的路径为那个文件夹,项目名字可以自己取(为了避免后面的不统一,建议和我取一样的) 从空项目创建 不用添加任何文件 选择开发板,我选择的是这个,然后ne…

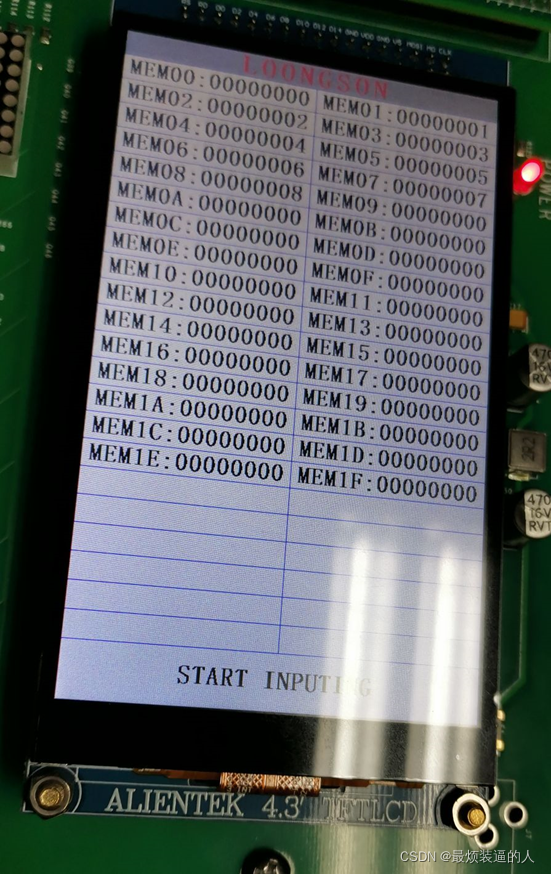

【单周期CPU】LoongArch | 32位寄存器DR | 32位的程序计数器PC | 通用寄存器堆Registers | 32位RAM存储器

前言:本章内容主要是演示在vivado下利用Verilog语言进行单周期简易CPU的设计。一步一步自己实现模型机的设计。本章先介绍单周期简易CPU中基本时序逻辑部件设计。

💻环境:一台内存4GB以上,装有64位Windows操作系统和Vivado 2017.…

「HDLBits题解」Cellular automata

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码 以提供参考 各位可同时参考我的代码和官方题解代码 或许会有所收益 题目链接:Rule90 - HDLBits

module top_module(input clk,input load,input [511:0] data,output [511:0] q );always (posedge clk) begin…

ASIC-WORLD Verilog(8)if-else语句和case语句

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----Asic-World网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文&…

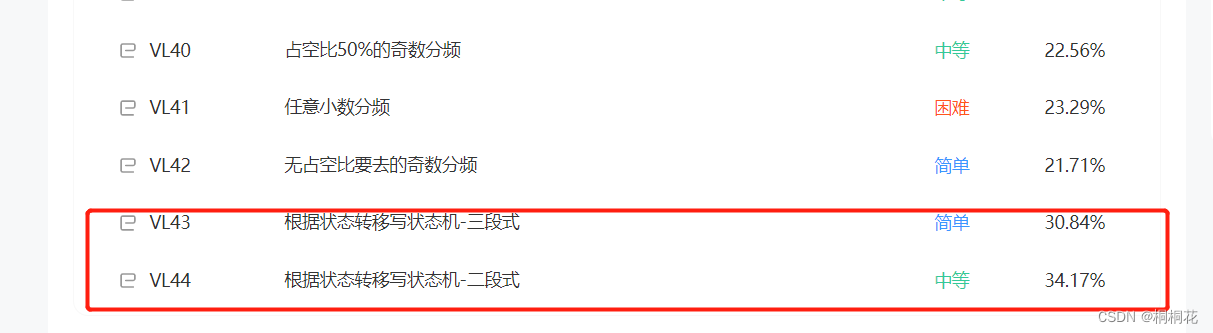

「Verilog学习笔记」根据状态转移写状态机-二段式

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 和三段式相比,就是将输出块和次态切换块合并。 timescale 1ns/1nsmodule fsm2(input wire clk ,input wire rst ,input wire data ,output reg flag

);//****…

「Verilog学习笔记」超前进位加法器

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 超前进位加法器的实质是:对于输出的每一位Si 其实都可以用Si Ai ^ Bi ^ Cin来表示 我们需要做的只是判断加法结果的最高位该取几 例如本题中 输入的两个数A和B…

verilog - signed 符号数与无符号

#verilog #FPGA

verilog - signed 符号数与无符号数计算 文章目录verilog - signed 符号数与无符号数计算原码 、反码 、 补码的关系verilog 中的 signed不同的扩位方式结论主要参考:

Verilog 中signed和$signed()的用法_长弓的坚持的博客-CSDN博客_$s…

新手--安装好Quartus II13.0(带modelsim集成包)并用Quartus II搭建一个工程

前言 今天是国庆节,我们正式来学习Quartus II13.0软件的安装与使用。学习verilog与学习C语言都是学习一门语言,那么学习一门语言,光看理论不敲代码绝对是学习不好的。要用verilog语言敲代码,就要像C语言那样搭建起语言的编译环境&…

IC工程师职场必备《经典Verilog100多个代码案例》(附下载)

对于IC行业的人员而言,Verilog是最基础的入门,用于数字电路的系统设计,很多的岗位都会用到,可对算法级、门级、开关级等多种抽象设计层次进行建模。

Verilog由于其简单的语法,和C语言的相似性,目前被各大公…

[Verilog] 加法器(半加法器 | 全加法器 | 串行加法器 | 并行加法器 | 十进制加法器)详解

前言 在数字电路中,加法器是一种常见的逻辑电路,用于将两个数字相加。本文将介绍如何使用Verilog实现各种加法器。

1 加法器种类

整数加法器 半加器(Half Adder):它是最简单的加法器,只能进行两个输入位的相加操作,不包括进位位。全加器(Full Adder):它是最基本的加…

51单片机学习笔记(清翔版)(23)——红外通讯

DS18B20课后题: 负数以补码形式存在的。 如果是负数,那么S全为1,前面那些不看,我们只看最后一个S,当它为1时,那么就是0x08,所以只要高8位大于等于0x08,就是负数。 其中s0x40这里 上面…

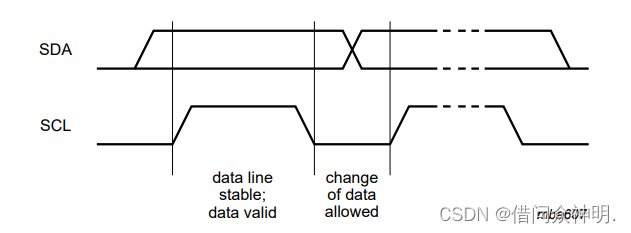

【FPGA】IIC协议主机接口的设计与实现详解

一、认识IIC IIC(I2C)协议是一种串行通信协议,用于连接微控制器和外围设备。IIC协议只需要两根信号线(时钟线SCL和数据线SDA)就能完成设备之间的通信;支持多主机和多从机通信,通过设备地址区分不…

HDLBits-Verilog学习记录 | Verilog Language-Vectors

文章目录 11.vectors | vector012.vectors in more detail | vector113.Vector part select | Vector214.Bitwise operators | Vectorgates15.Four-input gates | Gates416.Vector concatenation operator | Vector317.Vector reversal 1 | Vectorr18. Replication operator | …

两种fifo实现方式的差异

减少数据通路翻转来降低功耗: 以FIFO (当容量较小而使用寄存器作为存储部分)设计为例,虽然理论上可以使用比较简单的数据表项逐次移位的方式,实现FIFO 的先入先出功能,但是却应该使用维护读写指针的方式(数据表项寄存器则不用移位)实现先入先出的功能。因为数据表项逐次…

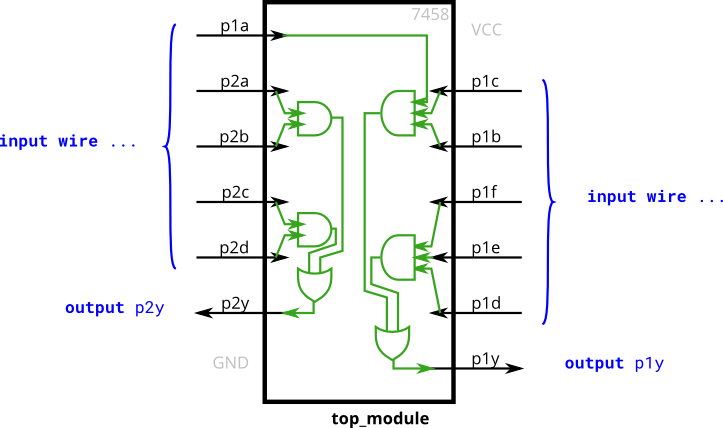

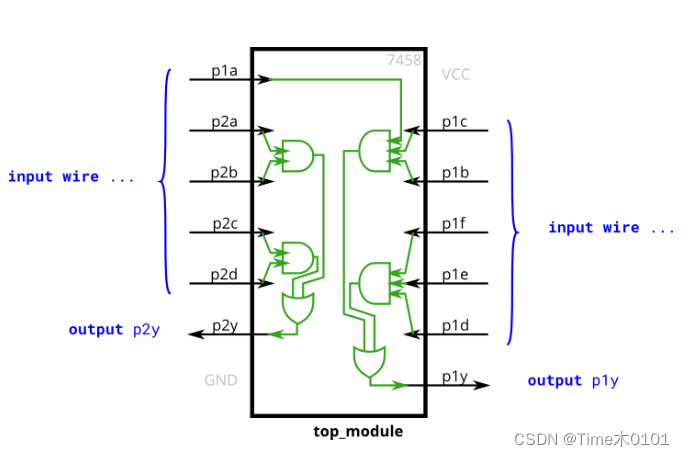

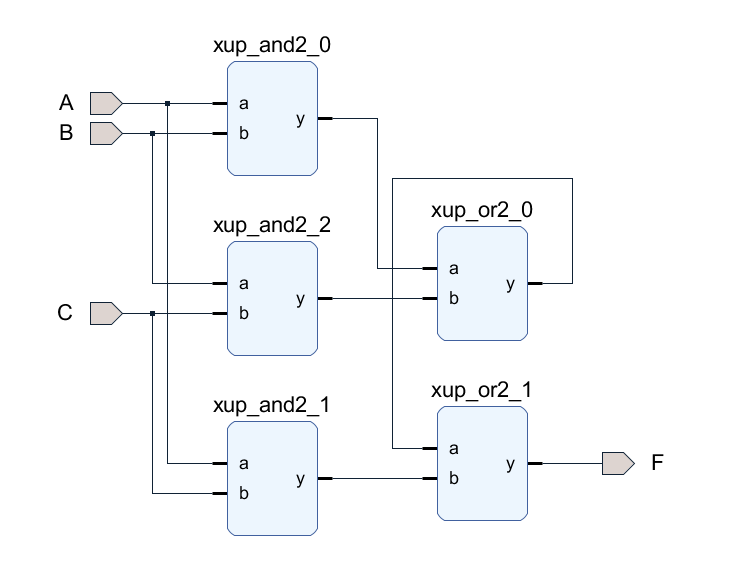

HDLBits-Verilog学习记录 | Verilog Language-Basics(2)

文章目录 9.Declaring wires | wire decl10. 7458 chip 9.Declaring wires | wire decl

problem:Implement the following circuit. Create two intermediate wires (named anything you want) to connect the AND and OR gates together. Note that the wire that feeds the …

【Verilog 教程】3.1 Verilog 连续赋值

关键词:assign, 全加器 连续赋值语句是 Verilog 数据流建模的基本语句,用于对 wire 型变量进行赋值。:

格式如下

assign LHS_target RHS_expression ;LHS(left hand side) 指赋值操作的…

[Verilog语言入门教程] 乘法器详解 与 设计/仿真

依公知及经验整理,原创保护,禁止转载。 专栏 《Verilog》 <<<< 返回总目录 <<<<

乘法器可以分为以下5种类型:

顺序乘法器(Sequential Multiplier):顺序乘法器是最简单的乘法器类型,采用逐位相乘的方法实现。这种乘法器适用于小规模的乘法运算…

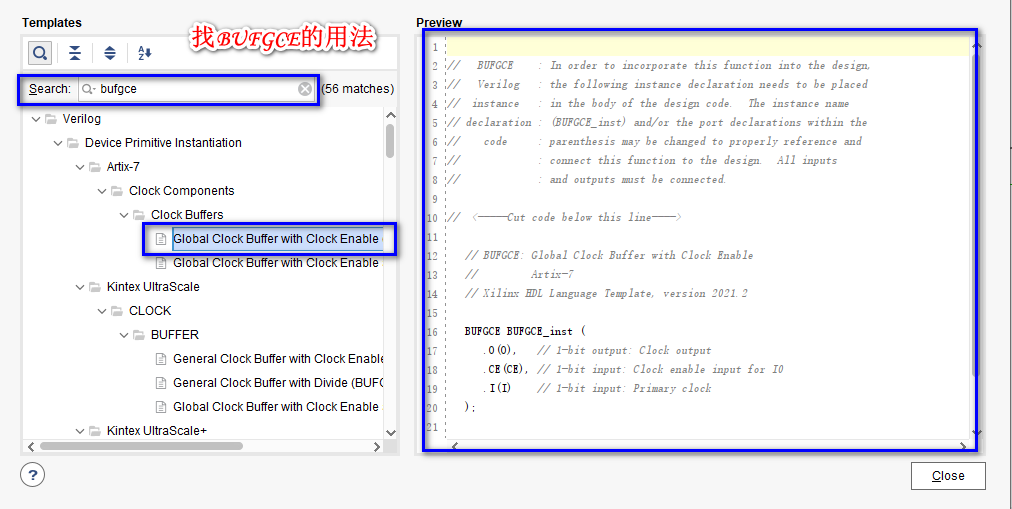

好的FPGA编码风格(2)--多参考设计软件的语言模板(Language Templates)

什么是语言模板? 不论是Xilinx的Vivado,还是Altera的Quartus II,都为开发者提供了一系列Verilog、SystemVerilog、VHDL、TCL、原语、XDC约束等相关的语言模板(Language Templates)。 在Vivado软件中,按顺序…

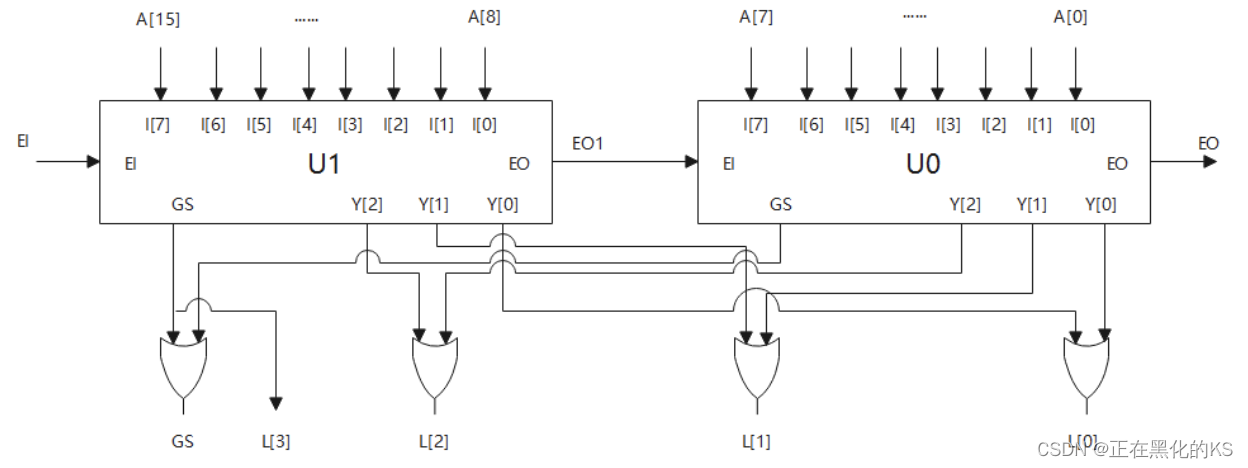

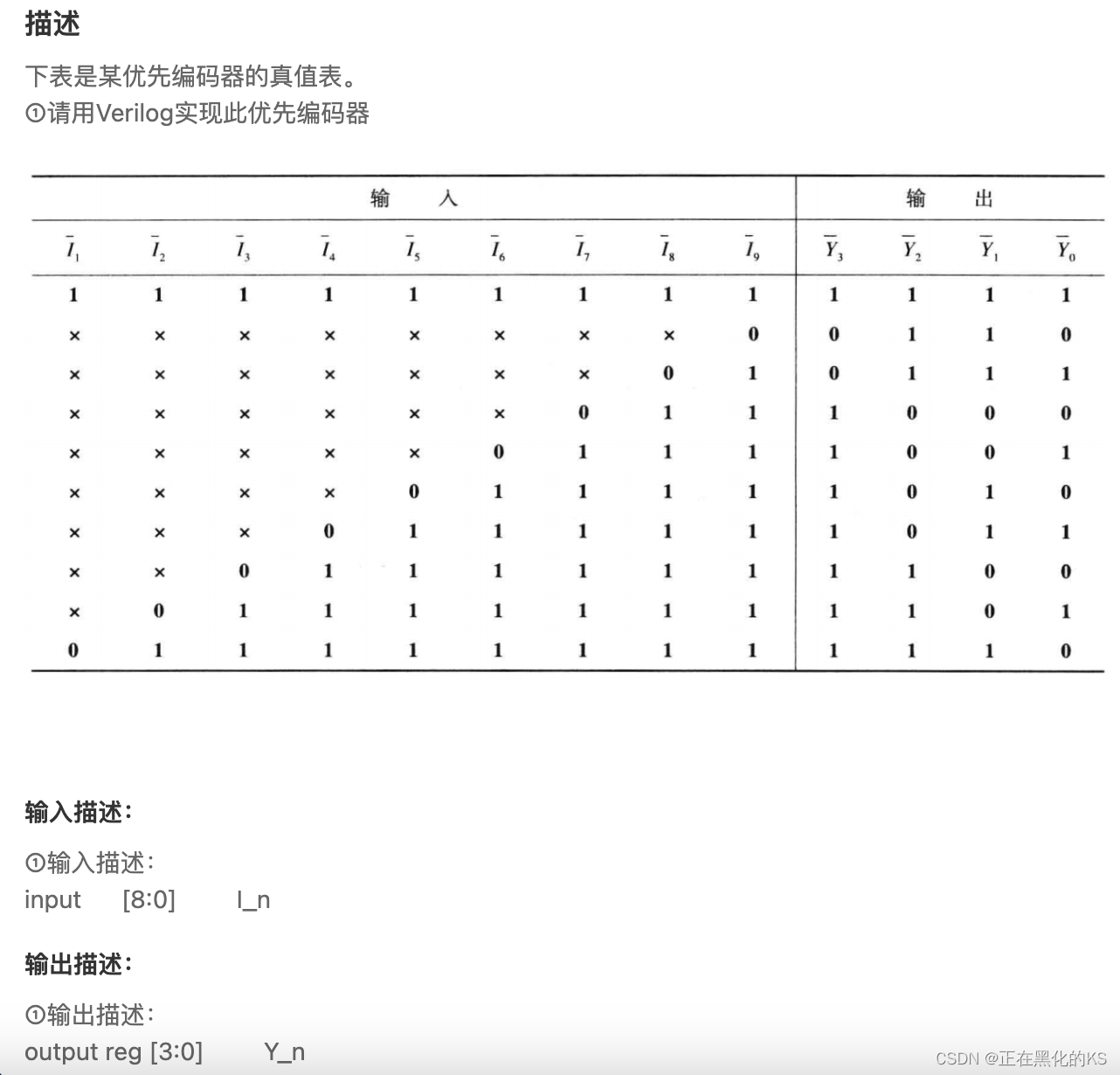

「Verilog学习笔记」使用8线-3线优先编码器Ⅰ实现16线-4线优先编码器

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 分析 当EI10时、U1禁止编码,其输出端Y为000,GS1、EO1均为0。同时EO1使EI00,U0也禁止编码,其输出端及GS0、EO0均为0。由电路…

Verilog实现2进制码与BCD码的互相转换

1、什么是BCD码?

BCD码是一种2进制的数字编码形式,用4位2进制数来表示1位10进制中的0~9这10个数。这种编码技术,最常用于会计系统的设计里,因为会计制度经常需要对很长的数字做准确的计算。相对于一般的浮点式记数法,…

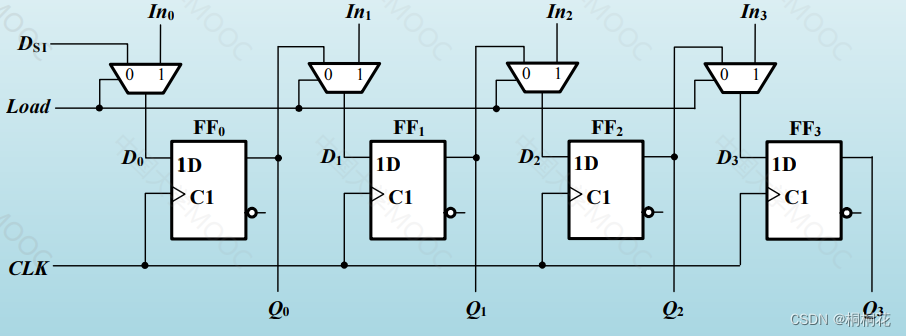

《计算机组成与CPU设计实验》3 时序逻辑(二)

移位寄存器

移位寄存器是什么?

将若干个D触发器串接级联在一起构成的具有移位功能的寄存器。

4位右移移位寄存器 原来输出 Q0 Q1 Q2 Q3

CLK上升沿到来

输出 Q0DSI Q1Q0 Q2Q1 Q…

【Verilog】期末复习——解释下列名词(FPGA、ASIC、IP、RTL、EDA、HDL、FSM)

系列文章

数值(整数,实数,字符串)与数据类型(wire、reg、mem、parameter) 运算符 数据流建模 行为级建模 结构化建模 组合电路的设计和时序电路的设计 有限状态机的定义和分类 期末复习——数字逻辑电路分…

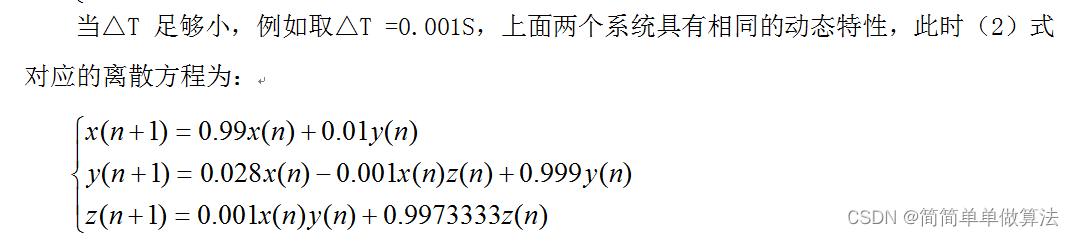

基于FPGA的Lorenz混沌系统verilog开发,含testbench和matlab辅助测试程序

目录

1.算法运行效果图预览

2.算法运行软件版本

3.部分核心程序

4.算法理论概述

5.算法完整程序工程 1.算法运行效果图预览 将vivado的仿真结果导入到matlab显示三维混沌效果: 2.算法运行软件版本

vivado2019.2

matlab2022a

3.部分核心程序

testbench如下所…

同步FIFO的verilog实现(1)——计数法

一、FIFO概述

1、FIFO的定义 FIFO是英文First-In-First-Out的缩写,是一种先入先出的数据缓冲器,与一般的存储器的区别在于没有地址线, 使用起来简单,缺点是只能顺序读写数据,其数据地址由内部读写指针自动加1完成&…

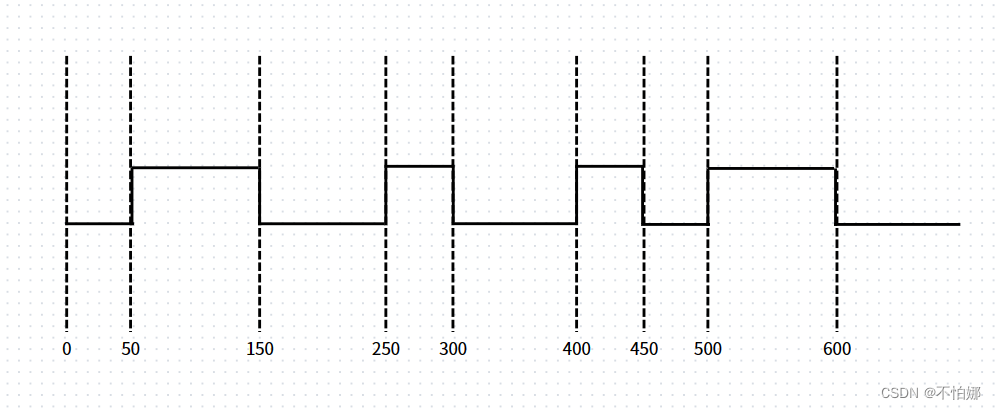

牛客网Verilog刷题——VL40

牛客网Verilog刷题——VL40 题目答案 题目 设计一个同时输出7分频的时钟分频器,占空比要求为50%。注意rst为低电平复位。 信号示意图如下: 波形示意图如下。 输入输出描述:

信号类型输入/输出位宽描述clk_inwireIntput1系统时钟信号rs…

用verilog实现边沿检测(上升沿,下降沿,双边)

不是很难却困扰过我的一个问题

边沿检测?不是可以直接把待检测的信号写在always块里吗?

其实不是的,这个题目的本意是在同步电路中实现这样的功能,如果把待检测的信号写在always块里面,相当于把输入信号接到了触发器…

51单片机学习笔记(清翔版)(13)——LED点阵、74HC595

如图3,点阵屏分单色和彩色,点阵屏是由许多点组成的,在一个点上,只有一颗一种颜色的灯珠,这就是单色点阵屏,彩色的在一个点上有三颗灯珠,分别是RGB三原色。 图4你可能没看出来,那么大…

Circuits--Combinational Logic--Basic Gates--Gates

网址:https://hdlbits.01xz.net/wiki/Gates

module top_module( input a, b,output out_and,output out_or,output out_xor,output out_nand,output out_nor,output out_xnor,output out_anotb

);assign out_and a & b;assign out_or a | b;assign out_xor …

Verilog基础:$time、$stime和$realtime系统函数的使用

相关阅读

Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html $time、 $stime和$realtime这三个系统函数提供了返回当前仿真时间方法。注意,这里的仿真时间的最小分辨能力是由仿真时间精度决定的,简单来说,可以理解为…

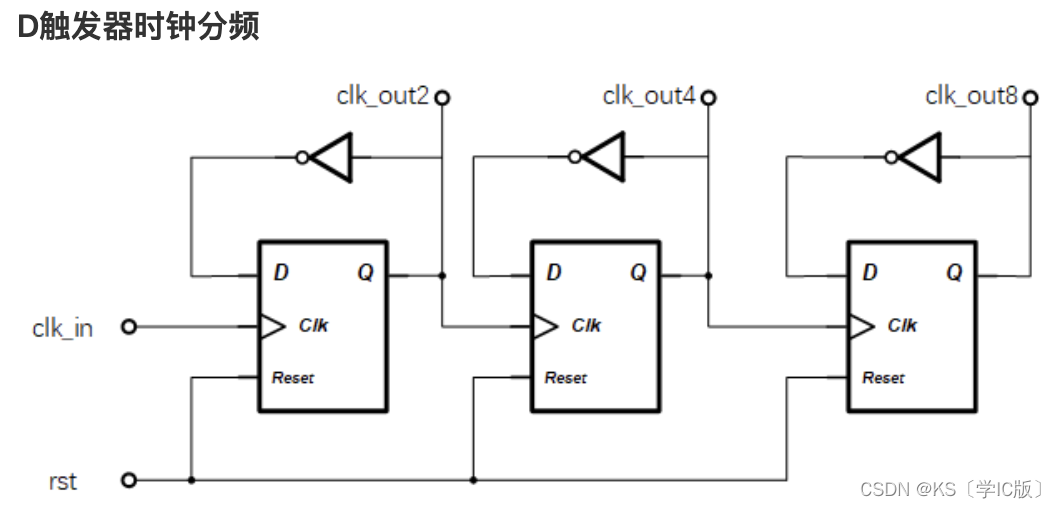

「Verilog学习笔记」时钟分频(偶数)

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 timescale 1ns/1nsmodule even_div(input wire rst ,input wire clk_in,output wire clk_out2,output wire clk_out4,output wire clk_out8);

//********…

「Verilog学习笔记」用优先编码器①实现键盘编码电路

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 分析 用此编码器实现键盘的编码电路。 注意:编码器的输出是低电平有效,而键盘编码电路输出的是正常的8421BCD码,是高电平有效。因此将编…

数字IC实践项目(9)— Tang Nano 20K: I2C OLED Driver

Tang Nano 20K: I2C OLED Driver 写在前面的话硬件模块RTL电路和相关资源报告SSD1306 OLED 驱动芯片SSD1306 I2C协议接口OLED 驱动模块RTL综合实现 总结 写在前面的话

之前在逛淘宝的时候偶然发现了Tang Nano 20K,十分感慨国产FPGA替代方案的进步之快;被…

跨时钟域异步FIFO设计verilog(一)FIFO原理介绍

本文大部分内容来自https://www.cnblogs.com/aslmer/p/6114216.html

本文首先对异步 FIFO 设计的重点难点进行分析 最后给出详细代码 设计一个异步FIFO,深度为8,位宽也是8. 代码是学习Simulation and Synthesis Techniques for Asynchronous FIFO Desig…

Verilog 高级教程笔记——持续更新中

Verilog advanced tutorial

转换函数

调用系统任务任务描述int_val $rtoi( real_val ) ;实数 real_val 转换为整数 int_val 例如 3.14 -> 3real_val $itor( int_val ) ;整数 int_vla 转换为实数 real_val 例如 3 -> 3.0vec_val $realtobits( real_val ) ;实数转换为…

基于FPGA的数字等精度频率计

传统的测频法原理

直接计数单位时间内被测信号的脉冲数。 在理想条件下:

门控时间基准时钟的整数倍,门控时间待测信号的整数倍,计数器检测上升沿

对照示意图,可得如下公式(1)(2)&a…

Vivado:ROM和RAM的verilog代码实现

本文主要介绍ROM和RAM实现的verilog代码版本,可以借鉴参考下。

一、ROM设计方法

Read-only memory(ROM)使用ROM_STYLE属性选择使用寄存器或块RAM资源来实现ROM,示例代码如下:

//使用块RAM资源实现ROM

module rams_s…

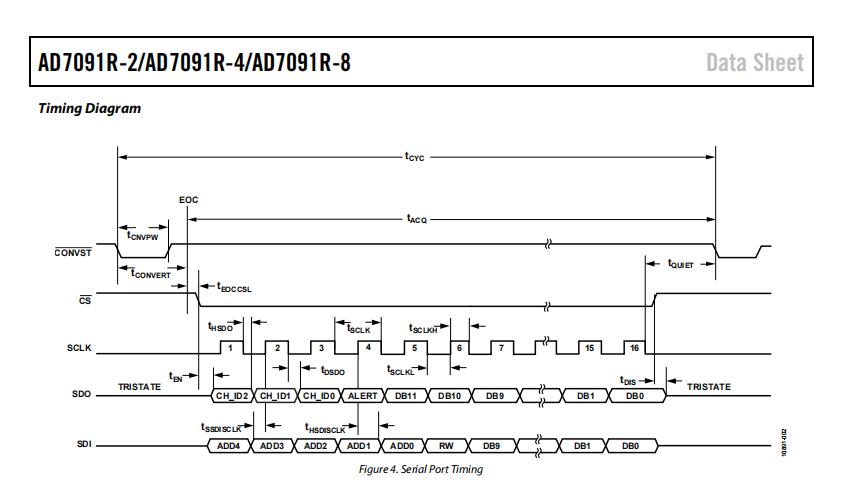

ADI模数转换AD7091的SPI驱动接口verilog,代码/视频

名称:ADI模数转换AD7091的SPI驱动

软件:QuartusII

语言:Verilog

代码功能:

完成ADI单通道模数转换器AD7091R的逻辑接口设计。1 MSPS、超低功耗、12-Bit ADC

(1)实现全部逻辑接口功能,完成对…

简单8位CPU设计verilog微处理器,源码/视频

名称:8位CPU设计微处理器

软件:QuartusII

语言:Verilog

代码功能: 设计一个简单的处理器,可以实现加减法以及简单的逻辑运算。 设计包括程序计数器电路,指令存储器电路,指令译码器电路(控制器…

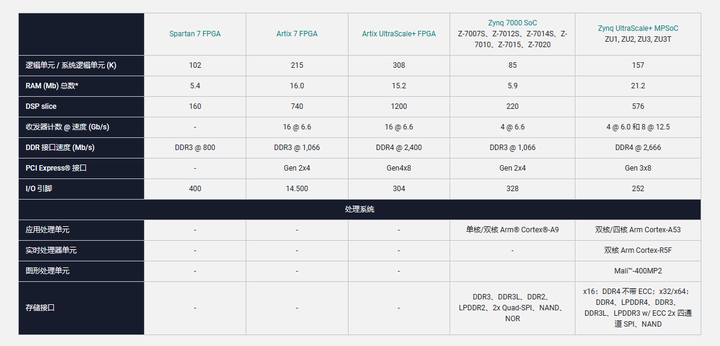

如何选对适合你的FPGA?快速掌握选型技巧!

FPGA厂家和芯片型号众多,在开发过程中,特别是新产品新项目时,都会面临FPGA选型的问题。

如何选择出适合的FPGA型号非常关键,需要评估需求、功能、成本、存储器、高速收发器等各种因素,选出性能与成本平衡的FPGA芯片。…

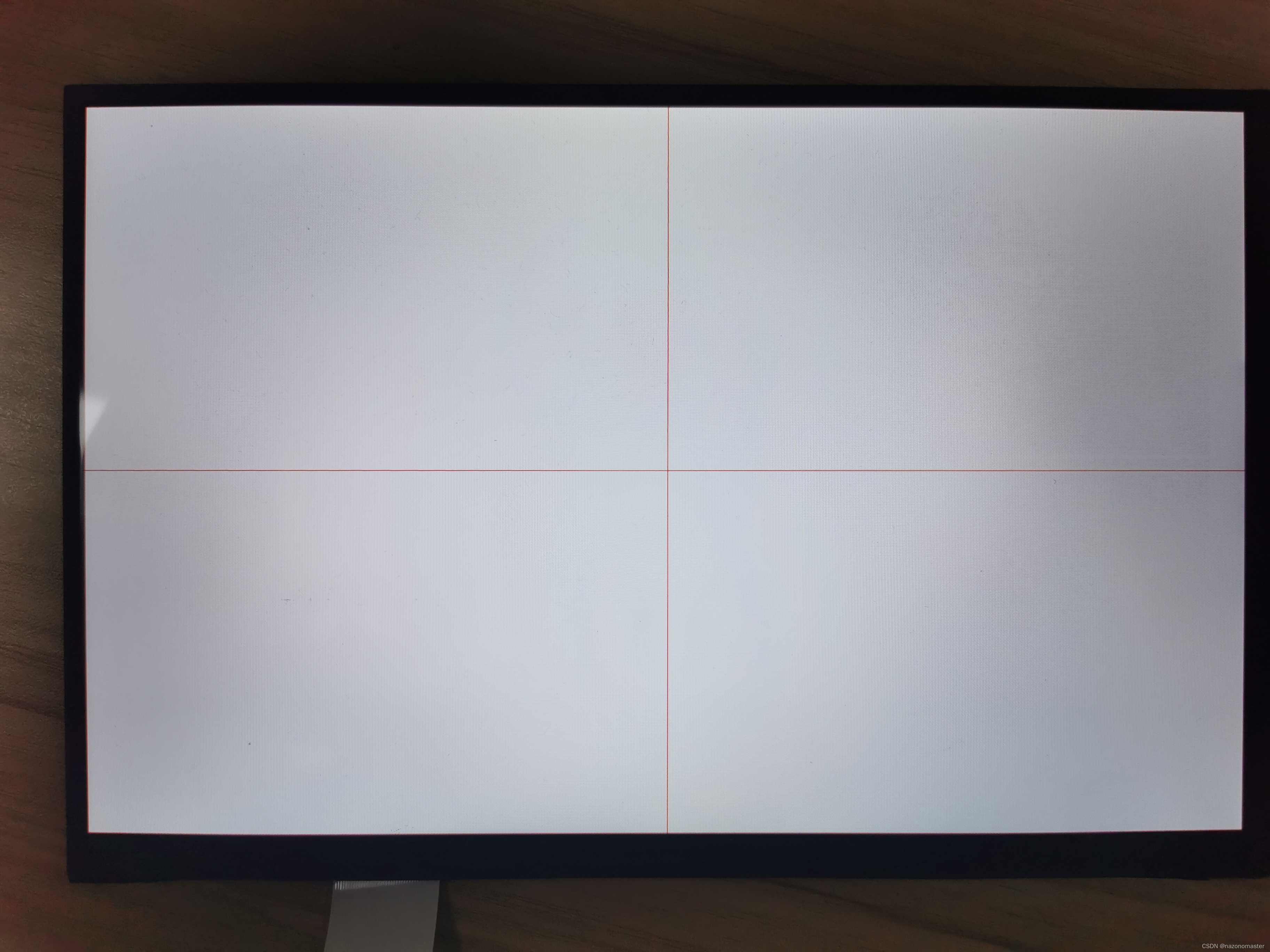

FPGA纯verilog实现任意分辨率视频输出显示,高度贴近真实项目,提供工程源码和技术支持

目录1、前言2、视频显示的VESA协议3、VESA协议的bug4、FPGA实现任意分辨率视频输出显示5、FDMA实现数据缓存6、vivado工程详解7、上板调试验证并演示8、福利:工程代码的获取1、前言

本设计使用纯Verilog代码实现,重点在于基于AXI协议的DDR控制器的运用&…

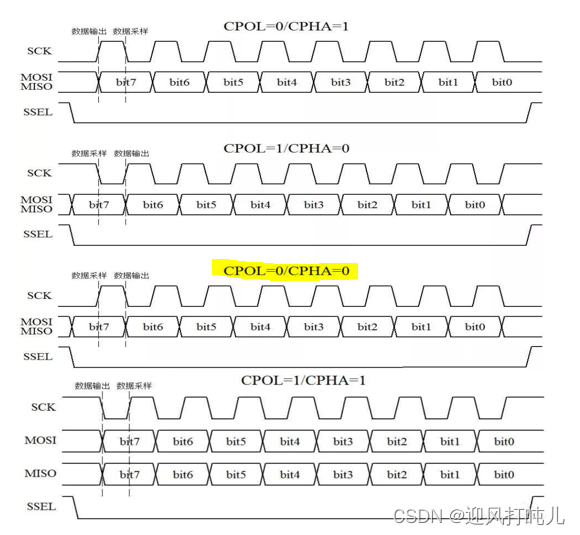

SPI接口的FPGA实现(一)——SPI接口的相关基础知识

SPI系列文章主要介绍SPI接口的一些基础知识,并用DAC芯片81416的配置为例来具体说明SPI接口的具体FPGA实现。

一、SPI的基础

SPI的全称是Serial Peripheral Interface,直译过来就是串行外围接口。一般情况下,FPGA连接各种DAC和ADC࿰…

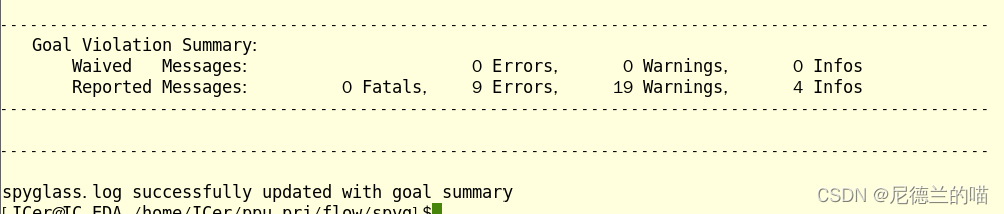

【HISI IC萌新虚拟项目】ppu模块基于spyglass的lint清理环境搭建与lint清理

关于整个虚拟项目,请参考: 【HISI IC萌新虚拟项目】Package Process Unit项目全流程目录_尼德兰的喵的博客-CSDN博客 前言

RTL代码在交付给验证同时进行功能验证时,可以同步进行lint的清理工作。一般而言影响编译和仿真的问题会在vcs的error和warning中被修正,因此清理lin…

HDLBits 刷题笔记 - Exams_ece241 2013 q8 - HDLBits

HDLBits 刷题笔记 - Exams_ece241 2013 q8 - HDLBits

题目原文:Exams/ece241 2013 q8 - HDLBits

题意 Implement a Mealy-type finite state machine that recognizes the sequence “101” on an input signal named x. Your FSM should have an output signal, …

ASIC-WORLD Verilog(3)第一个Verilog代码

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的Verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文…

大端小端,LSB和MSB

在verilog中碰到了lsb和msb,所以做一下解释:

lsb 就是最低位有效,类似于wire [0:31]这样的顺序。

msb 就是最高位有效,类似于wire [31:0]这样的顺序。还有计算机中还有大端小端的概念一块解释一下:举例:0X…

按键延迟时间测试的Verilog实现(FPGA实验)

本次实验目的在于熟悉状态机的控制,需要实现的功能如下: 按下按键并保持然后松开 当保持时间小于1s时,一个led灯闪烁2次。 当保持时间小于2s大于1s时,一个led灯闪烁4次。 当保持时间大于2s时,四个led灯闪烁4次。 本次实…

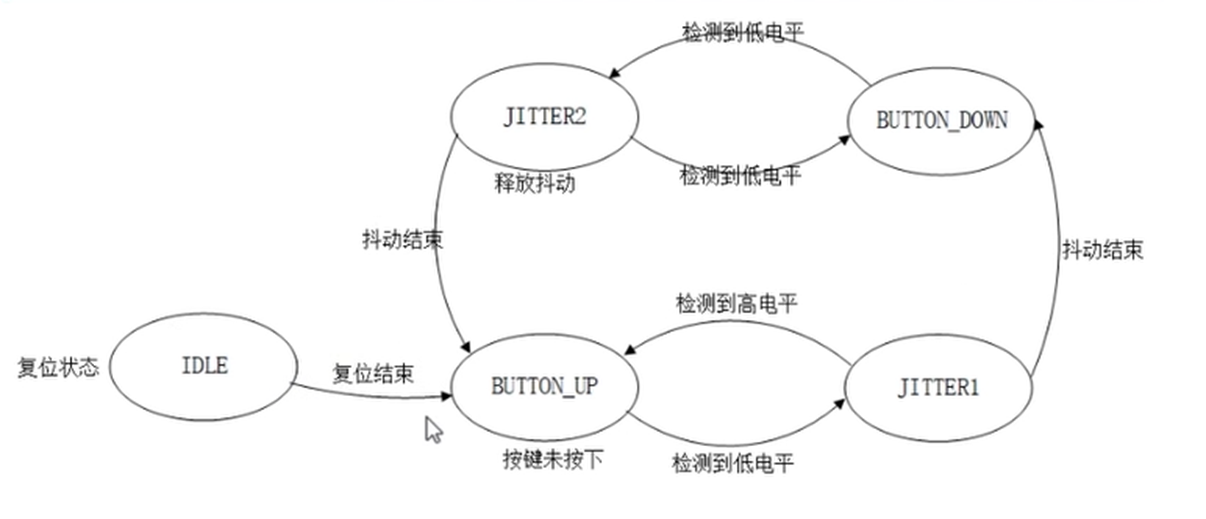

按键消抖的Verilog实现

由于普通物理按键存在反作用弹簧,因此当按下或者松开时均会产生额外的物理抖动,物理抖动便会产生电平的抖动。在按键从按下再到松开的过程中,其电平变化如图1所示,上为理想波形输出,下为实际波形输出。 因此࿰…

奇数分频电路—5分频(verilog实现)

文章目录前言占空比不为50%的奇数分频占空比为50%的5分频电路扩展前言

前文我们讲到,可以通过计数器的方法实现偶数分频,实现方式可以参考4分频电路实现 那么对于奇数分频电路应该如何实现呢?是否也可以通过计数器实现呢?答案是肯…

序列检测器Verilog设计

检测10010的串

timescale 1ns/10ps

module listcheck (rst,clk,in,result);

input rst,clk;

input in;

output result;

reg out;

assign result out;

reg [2:0] current_state,next_state;

parameter [2:0]S0 3b000,S1 3b001,S2 3b010,S3 3b011,S4 3b100,S5 3b101;

//s…

消除毛刺的两级缓冲器设计

module glitch(clk,data,q_out);

input clk,data;

output reg q_out;

reg q1;always(posedge clk)

beginq1 < data;

endalways(posedge clk)

beginq_out < q1;

endendmodule

自动饮料售卖机Verilog设计

饮料为5美分,饮料机只能接收1美分,2美分,5美分的钱币,请设计一个Verilog电路表示

timescale 1ns/10ps

module sell(one,two,five,rset,clk,result);

input one,two,five,rset,clk;

output result;

reg drink;

assign result dri…

三分频电路Verilog设计

三分频用两个在不同的时钟沿的序列发生器来构成一个3分频信号:

timescale 1ns/10ps

module div_3(clkin,clkout1,clkout2,clkout3);

input clkin;

output clkout1,clkout2,clkout3;

reg [1:0] step1,step0;

always (posedge clkin)

begincase(step0)2b00: step0 &l…

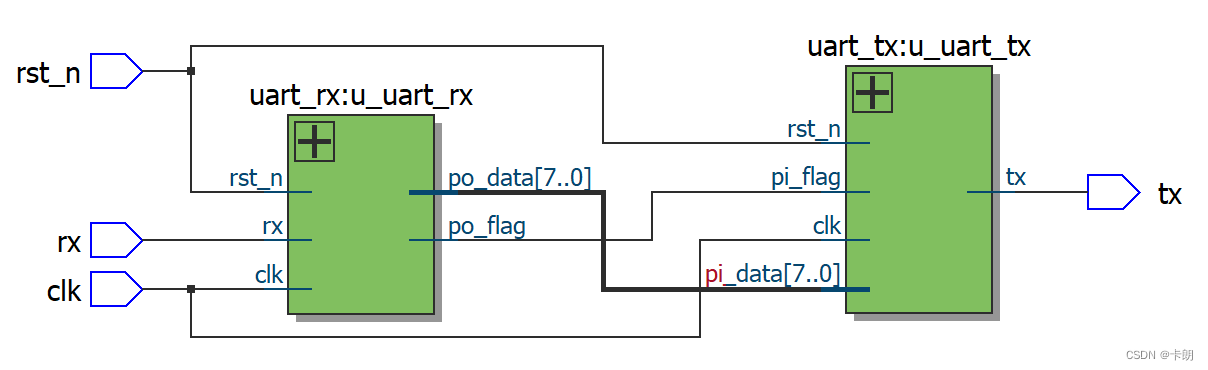

【FPGA】FPGA实现UART串口通信回环

目录一、UART协议基础二、系统模块划分三、代码实现1、uart顶层设计模块2、uart_rx串口数据接收模块3、control控制模块4、uart_tx串口数据发送模块四、仿真五、上板验证六、踩坑事项一、UART协议基础

关于UART协议的基础理论部分已经在上一篇文章中讲述,不再重复介…

verilog 入门教程

verilog 入门教程 1.1 什么是Verilog HDL? 1.2 Verilog的历史 1.3 Verilog的主要描述能力 2.1 Verilog-模块 2.2 Verilog-时延 2.3 Verilog-assign语句 2.4 Verilog-initial语句 2.5 Verilog-always语句 2.6 Verilog的结构化描述形式 2.7 Verilog-混合设计描述方式 2.8 Veri…

静态时序分析简明教程(五)]生成时钟的sdc约束方法

STA的时钟常规约束一、写在前面1.1 快速导航链接二、生成时钟2.1 标识时钟源2.2 时钟命名2.3 设定生成时钟的特性2.3.1 -edges2.3.2 -divide_by2.3.3 -invert2.3.4 -multiply_by2.3.5 时钟沿位移2.4 多个同源时钟2.5 使能组合电路路径2.6 注释时钟三、总结一、写在前面

一个数…

工具:为Verilog状态机自动生成状态定义代码

工具:为Verilog状态机自动生成状态定义代码 更新历史 20200411: 首次发布 作为一名电子学工程师,FPGA的逻辑开发是少不了的。用Verilog开发FPGA逻辑时,我发现:

状态机中的状态数量很多时,状态定义代码写起…

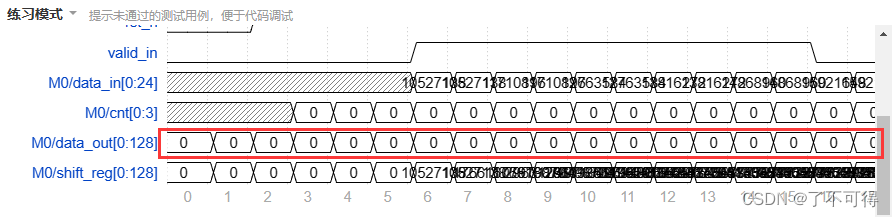

【23】Verilog进阶 - 数位转换【实时处理 + 标志信号】

【初次尝试】VL32 非整数倍数据位宽转换24to128

1 理解题目含义

根据【模块端口】和【题目描述】本题的真实意思是比较清楚啦。但不可大意轻敌!

(1)问题1:输出一直为0

猛然间发现计数值也为0,没有增加 去排查cnt的代码,很容易找到到问题,是cnt上电复位的逻辑写错了 …

Verilog与VHDL的一些比较

1.列表

verilogVHDLincludeLIBRARY IEEEmoduleENTITYarchitecturealwaysprocesswire/regsignalassign<阻塞-组合逻辑<非阻塞-时序逻辑posedge clk(negedge)clk’event and clk ‘1’

2.图例 图例来源网络,有空可以敲一遍

Verilog实现按键消抖(状态机方法)

文章目录按键抖动分析按键消抖逻辑Verilog设计与仿真Modelsim工程下载按键抖动分析 常用的轻触按键内部结构为金属弹片,在手按下、松开的过程中往往会发生细微抖动。 输出的逻辑电平也会发生快速翻转,按键按下和释放的过程中,都会产生抖动&a…

Verilog学习笔记1——关键词、运算符、数据类型、function/task、initial/always、generate

文章目录前言一、关键词二、运算符三、数据类型1、基本类型:reg、wire、integer、parameter四、条件语句五、循环语句1、for2、generate六、function和task七、initial和always1、initial和always相同点和区别2、always和assign语句区别前言

2023.4.4 2023.4.7 补充…

FPGA RTL开发中使用到的VSCode编辑插件安装讲解

实验概况

安装VScode软件及各个支持库,完成对Verilog代码自动补全和语法错误检查。

实验目的

熟悉软件安装方法,为开发做好充足准备

软件

VScode、以及各个插件

硬件

电脑

目录

第一讲、VScode编辑器软件安装1

1.软件基本介绍:2

2…

Verilog Tutorial(8)循环语句

写在前面在自己准备写verilog教程之前,参考了许多资料----FPGA Tutorial网站的这套verilog教程即是其一。这套教程写得不错,只是没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。这是网站原文:h…

verilog 并列 连续赋值

当事件发生时,对于代码块中的非阻塞赋值语句,先计算所有非阻塞语句在【事件发生时刻】的值,(即以<右端表达式的值),最后才把计算出的值赋给<左边的变量。 计算过程是以代码块中语句的书写顺序进行。虽有先后顺序,…

RAM Sequential

前段时间,在微信公众号上偶然看到一篇很不错的技术分享文章:《南湖处理器DFT设计范例》。文中详细介绍了中科院计算所的RISC-V处理器实施的DFT设计。 去年,也基于一款处理器应用过Share Test Bus技术,但在memory界面fault测试的问…

HDLBits-Verilog Language-Modules:Hierarchy(模块:层次结构)

目录 Module shift8 Module shift8

This exercise is an extension of module_shift. Instead of module ports being only single pins, we now have modules with vectors as ports, to which you will attach wire vectors instead of plain wires. Like everywhere else i…

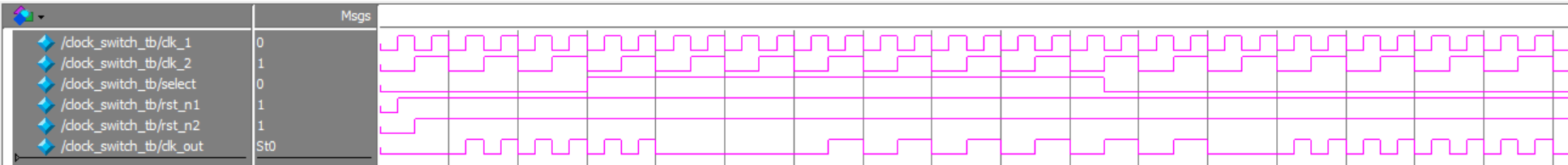

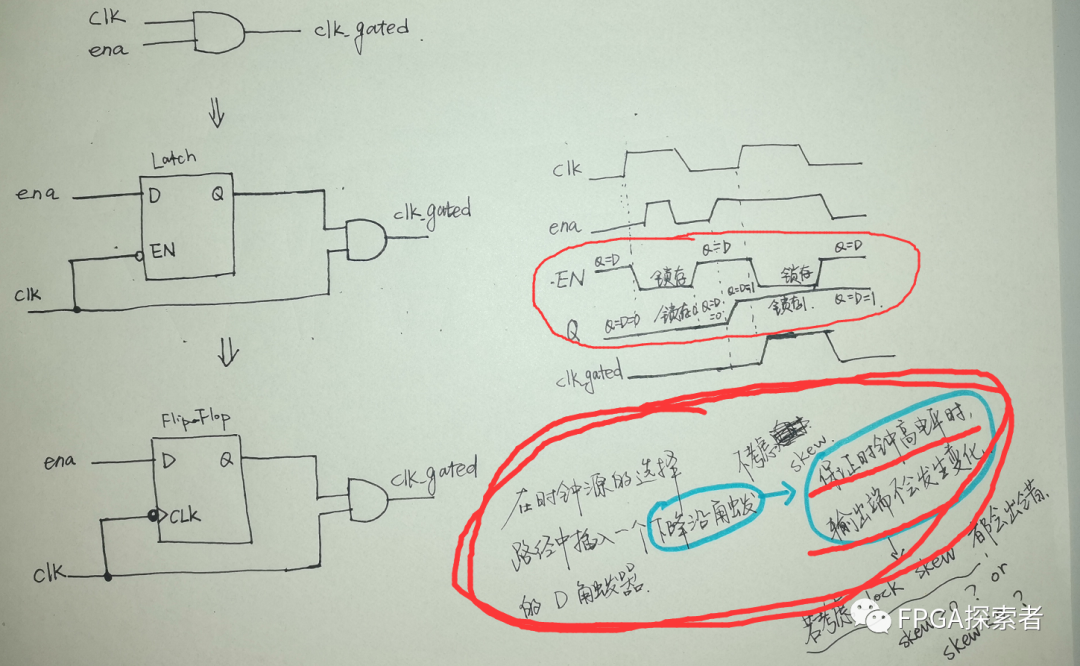

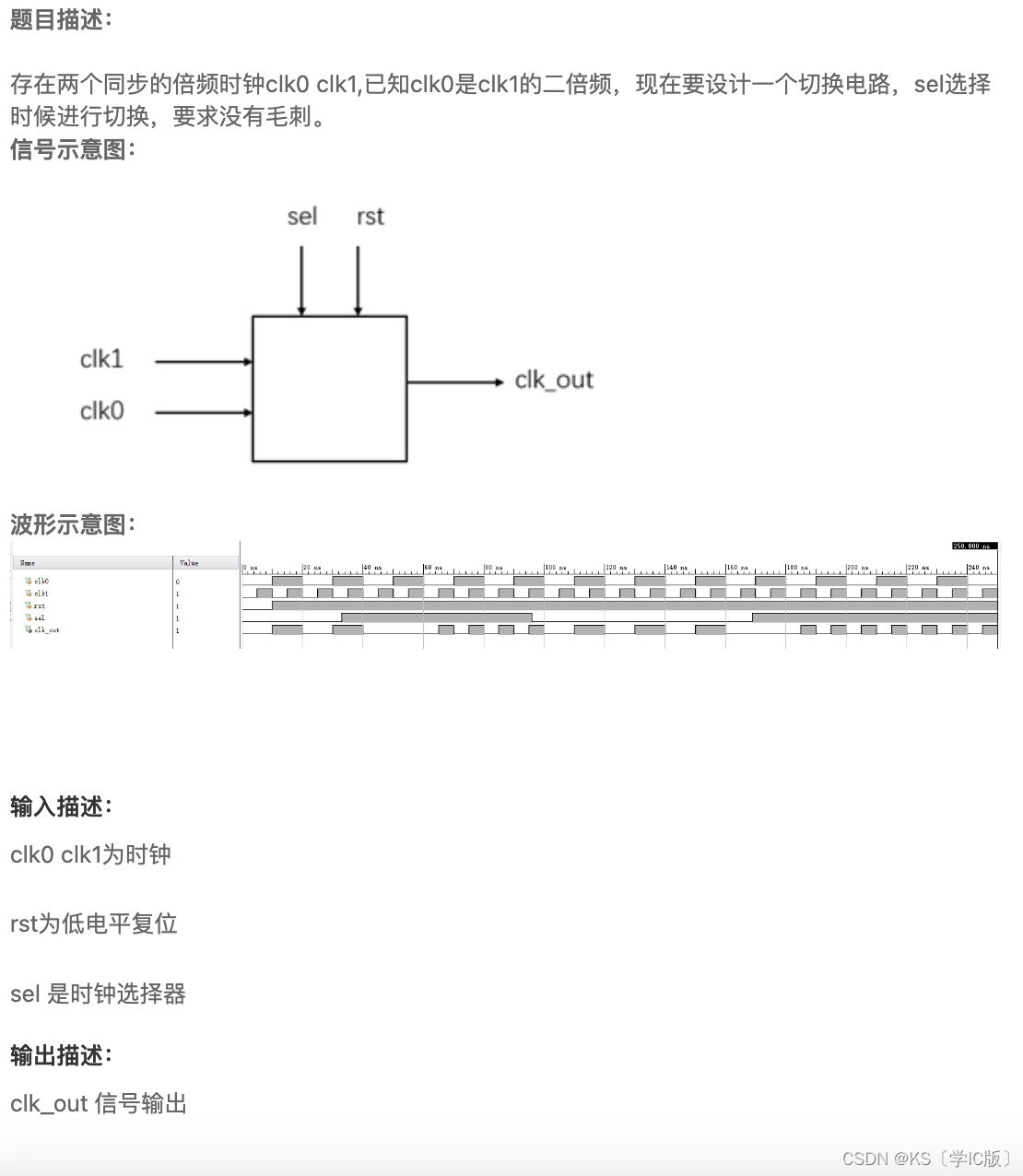

数字IC前端学习笔记:时钟切换电路

相关阅读

数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm1001.2014.3001.5482 有些时候我们需要在系统运行时切换系统时钟,最简单的方法就是使用一个MUX(数据选择器)选择输出的时钟,如下代码片所…

【Verilog】期末复习——VerilogHDL描述数字逻辑电路的建模方式有哪三种?它们的特点是?

系列文章

数值(整数,实数,字符串)与数据类型(wire、reg、mem、parameter) 运算符 数据流建模 行为级建模 结构化建模 组合电路的设计和时序电路的设计 有限状态机的定义和分类 期末复习——数字逻辑电路分…

【Verilog】期末复习——设计带异步清零且高电平有效的4位循环移位寄存器

系列文章

数值(整数,实数,字符串)与数据类型(wire、reg、mem、parameter) 运算符 数据流建模 行为级建模 结构化建模 组合电路的设计和时序电路的设计 有限状态机的定义和分类 期末复习——数字逻辑电路分…

【4分频电路 -verilog】

分频器介绍

分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分&#…

【$fopen函数的用法】

文章目录语法介绍uvm中的用法语法介绍 $fopen函数的功能是使用给定的模式 mode 打开 filename 所指向的文件。文件顺利打开后,指向该流的文件句柄就会被返回。如果文件打开失败则返回 0。 $fopen函数格式如下: <file_desc> $fopen("", …

FPGA的通用FIFO设计verilog,1024*8bit仿真,源码和视频

名称:FIFO存储器设计1024*8bit

软件:Quartus

语言:Verilog

本代码为FIFO通用代码,其他深度和位宽可简单修改以下参数得到

reg [7:0] ram [1023:0];//RAM。深度1024,宽度8

代码功能:

设计一个基于FPGA…

数字芯片设计——出窗

前言:在图像处理和AI算法领域,由于经常需要与卷积核进行卷积运算,所以需要对串行数据进行出窗处理,比如对输入信号进行缓存,之后输出一个N*N大小的窗口,本文主要讲解缓存出窗的常用思路。

需求

对串行输入…

【不重叠序列检测-状态机方法实现】

文章目录题目描述解题思路:状态转移图dut和tb代码:波形图题目描述

编写一个序列检测模块,检测输入信号(a)是否满足011100序列, 要求以每六个输入为一组,不检测重复序列,例如第一位数…

简单电子琴设计verilog蜂鸣器8音阶,视频/代码

名称:简单电子琴设计verilog

软件:QuartusII

语言:Verilog

代码功能:

简易电子琴电路

1、输入为8个按键,每个按键对应一个音阶

2、输出为speaker蜂鸣器,当其中一直按键按下时,输出特定频率…

【verilog---- if else 与多if 代码综合电路区别】

if else 与多if 代码综合电路区别if else形式多if形式if else形式

if else 形式写的代码会被EDA软件综合为多路选择器,无优先级顺序。

/** Author: yaohao * Date: 2022-11-21 15:22:20 * Last Modified by: yaohao* Last Modified time: 2022-11-21 15:49:56*/mo…

FPGA项目(16)——基于FPGA的音乐演奏电路

1.设计要求 能在实验箱上,循环播放一段音乐。(需要源码的直接看最后一节) 2.设计原理 组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能连续演奏所需要的两个基本要素,问题是如何来获取这两个要素所对应的数值以及通过纯硬件…

【sv中枚举类型与字符串语法学习】

文章目录枚举基本语法类型转换枚举类型内置方法字符串内置方法枚举

基本语法

枚举类型可以用来声明一组整型的命名常量,定义具有强类型的枚举变量。枚举类型还可以使用枚举名字而不是枚举值来方便地引用或显示。当没有指定数据类型的时候,缺省的数据类…

verilog HDL -生成块 - generate——endgenerate

参考:vrilog数字系统设计 夏宇闻 【第3版】 5.7

生成块理解 生成语句可以动态的生成verilog代码,方便参数化模块的生成,大大的简化程序的编写过程,常用于以下情况:

对矢量中的多个位进行重复操作进行多个模块的实例引用的重复操…

音乐播放器蜂鸣器AX301开发板verilog,视频/代码

名称:音乐播放器蜂鸣器播放音乐按键切歌

软件:Quartus

语言:Verilog

代码功能: 设计一个音乐播放器,使用板子上的蜂鸣器播放歌曲,可以播放三首歌(歌曲任选),通过按键控…

「HDLBits题解」Wire

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码 以提供参考 各位可同时参考我的代码和官方题解代码 或许会有所收益 题目链接:Wire - HDLBits

module top_module( input in, output out );assign out in ;

endmodule

gvim中进行verilog语言信号追踪、显示拓扑插件

插件使用方法及功能:

vtags 是一款在gvim下实现类似verdi的信号追踪、显示拓扑等功能的插件。vtags插件完全使用python实现,目前实现功能包括信号追踪、宏定义追踪、显示模块拓扑、快速打开文件、保存和打开gvim快照、添加断点等功能。

支持功能和快捷…

verilog读取bmp格式图片

代码如下: timescale 1 ns/1 ns

module test_t;

integer fileId, cc,out_file,i;

reg [7:0] bmp_data [0:2000000];

reg clk;

reg [7:0] data;

integer bmp_width, bmp_hight, data_start_index, bmp_size; initial

beginfileId $fopen("G:\\Contrast ratio\\part_var\\…

【USTC】verilog 习题练习 36-40

36 条件运算符

题目描述

Verilog中有一个跟C语言中类似的三目条件运算符( ? : ),其语法格式为: (condition ? if_true : if_false) 该表达式可以用于为其它信号赋值,例如:signal condition ? if_true : if_fals…

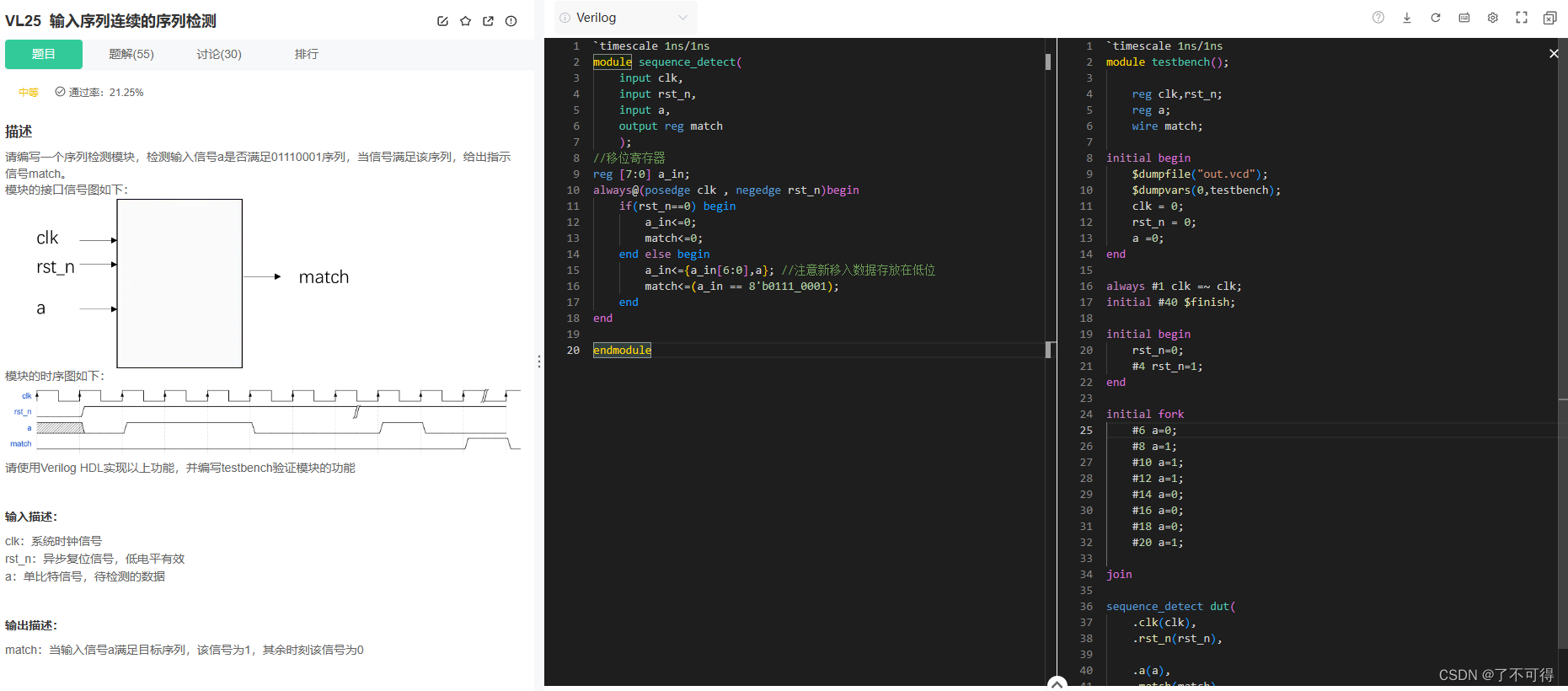

【25】Verilog进阶 - 序列检测

VL25 输入序列连续的序列检测

本题并不难【中等】难度给高了 【做题关键】 (1)需要使用移位寄存器的思路。其实reg型是寄存器,也可以当做是移位寄存器,重要的是对其的处理,使用的是移位寄存器的思路 (2)注意新移入数据存放在低位

1 题目 + 代码 + TestBench 很简单,没…

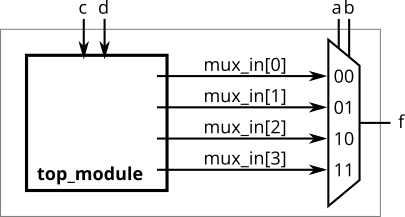

【USTC】verilog 习题练习 21-25

21 基于端口名称的实例化

题目描述

创建一 verilog 电路,实现对模块 mod_a 基于端口名称的实例化,如下图所示: 其中mod_a模块的代码为:

module mod_a (output out1,output out2,input in1,input in2,input in3,in…

「HDLBits题解」Gates100

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码 以提供参考 各位可同时参考我的代码和官方题解代码 或许会有所收益 题目链接:Gates100 - HDLBits

module top_module( input [99:0] in,output out_and,output out_or,output out_xor

);assign out_and &…

通用FIFO设计深度8宽度64,verilog仿真,源码和视频

名称:通用FIFO设计深度8宽度64,verilog仿真

软件:Quartus

语言:verilog

本代码为FIFO通用代码,其他深度和位宽可简单修改以下参数得到

reg [63:0] ram [7:0];//RAM。深度8,宽度64

代码功能:…

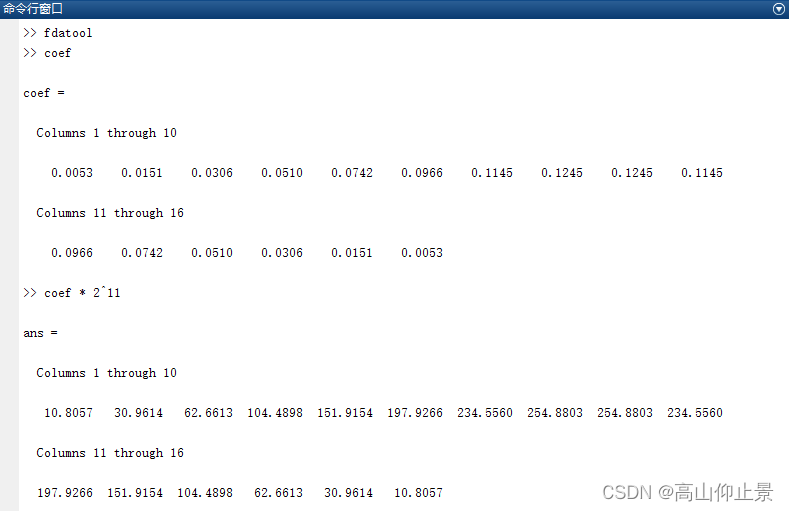

FPGA设计FIR滤波器低通滤波器,代码及视频

名称:FIR滤波器低通滤波器

软件:Quartus

语言:Verilog/VHDL

本资源含有verilog及VHDL两种语言设计的工程,每个工程均可实现以下FIR滤波器的功能。 代码功能:

设计一个8阶FIR滤波器(低通滤波器ÿ…

Verilog刷题[hdlbits] :Always case2

题目:Always case

A priority encoder is a combinational circuit that, when given an input bit vector, outputs the position of the first 1 bit in the vector. For example, a 8-bit priority encoder given the input 8’b10010000 would output 3’d4, b…

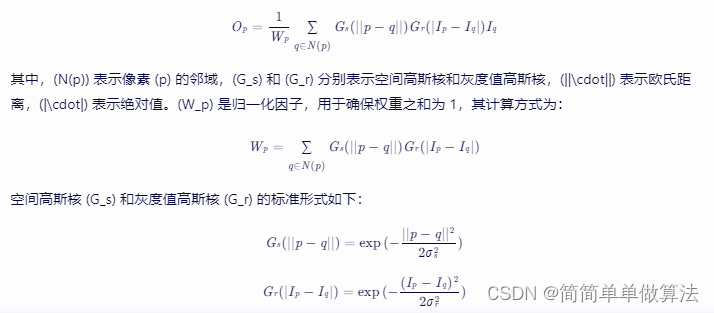

基于FPGA的图像双边滤波实现,包括tb测试文件和MATLAB辅助验证

目录

1.算法运行效果图预览

2.算法运行软件版本

3.部分核心程序

4.算法理论概述

4.1 双边滤波数学模型

4.2 双边滤波的特性

4.3 FPGA实现架构

5.算法完整程序工程 1.算法运行效果图预览 将FPGA数据导入到matlab对比测试: 2.算法运行软件版本

vivado2019.2 …

【基于APB总线的DES实现】

基于APB总线的DES实现 本文内容摘要APB介绍仿真结果整体仿真写入数据DES加密部分DES加密读出密文 整体代码 本文内容摘要 本文是设计一个可兼容APB总线的DES加密协处理器,用来将DES加密模块与APB总线进行对接,使总线发送来的数据可以正常写入并进行加密后…

「HDLBits题解」Build a circuit from a simulation waveform

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码 以提供参考 各位可同时参考我的代码和官方题解代码 或许会有所收益 题目链接:Sim/circuit1 - HDLBits

module top_module (input a,input b,output q );//assign q a & b ; // Fix meendmodule题目链接&a…

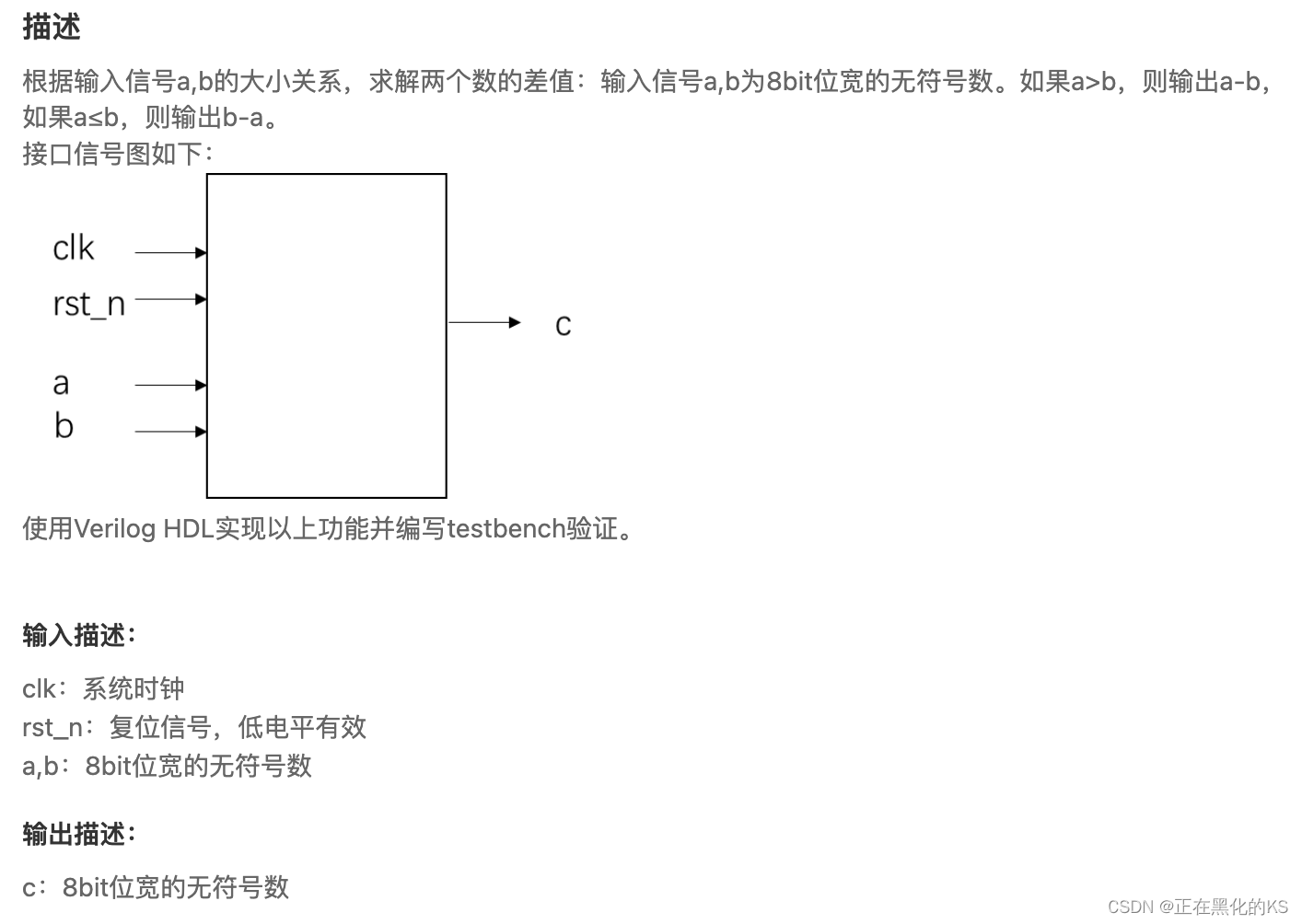

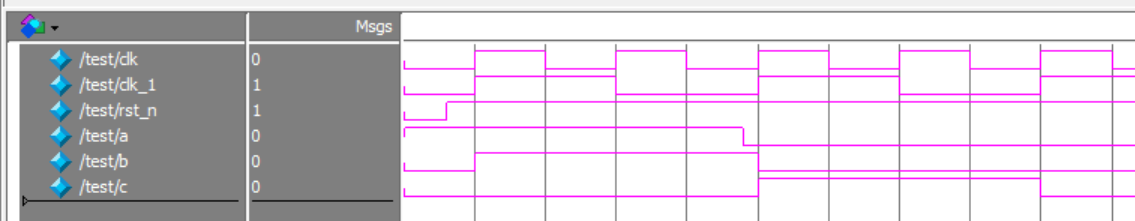

「Verilog学习笔记」求两个数的差值

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 timescale 1ns/1ns

module data_minus(input clk,input rst_n,input [7:0]a,input [7:0]b,output reg [8:0]c

);always (posedge clk or negedge rst_n) begin if (~rst_…

二分频电路Verilog设计

2分频电路设计

timescale 1ns/10ps

module div_2(clk,rst,out);

input clk,rst;

output out;reg q;

always(posedge clk or negedge rst)if(!rst)q<1b0;elseq<~q;

assign outq;

endmodule

测试程序:

module div_2_tb();

reg clk,rst;

wire out;

div_2 wt (…

Golang-如何优雅的关闭channel?

如何优雅的关闭channel? channel关闭原则 "如何优雅的关闭channel?",这种问题经常在面试题中出现,究其原因,是因为channel创建容易,但是关闭"不易",原因有以下三点…

quartus15+modelsim使用关键步骤笔记

参考视频:零基础轻松学习FPGA,小梅哥FPGA设计思想与验证方法视频教程_哔哩哔哩_bilibili

1、新建工程 2、编译检查 3、运行仿真

先添加好路径 再改一下设置 再运行仿真 ,记得顶层模块要置顶 4、RTL电路综合 5、状态图查看

「Verilog学习笔记」根据状态转移写状态机-三段式

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 状态机可以分为Moore状态机和Mealy状态机。 Moore状态机:输出只由当前状态决定Mealy状态机:输出由当前状态和当前的输入共同决定。 三段式状态机是指…

Verilog基础:时序调度中的竞争(二)

相关阅读

Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html?spm1001.2014.3001.5482 作为一个硬件描述语言,Verilog HDL常常需要使用语句描述并行执行的电路,但其实在仿真器的底层,这些并行执行的语句是有先后顺序…

《Clock Domain Crossing》 翻译与理解(5)多信号跨时钟域传输

本系列将对sunburst design网站的2008最佳文章《Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog》进行翻译和基于自我理解的分析阐述,本文介绍多信号跨时钟域传输。

目录

多信号跨时钟域传输

多比特 CDC策略

多比特信号…

《Clock Domain Crossing》 翻译与理解(4)快时钟到慢时钟数据传输

本系列将对sunburst design网站的2008最佳文章《Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog》进行翻译和基于自我理解的分析阐述,本文介绍快满时钟数据传输问题。

慢时钟到快时钟

慢时钟数据传递到快时钟域时&#x…

《Clock Domain Crossing》 翻译与理解(2)打两拍

前言:本系列将对sunburst design网站的2008最佳文章《Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog》进行翻译和基于自我理解的分析阐述,本文将介绍打两拍同步器。

同步器

“同步器是一种对异步信号进行采样…

10进制计数器Verilog编程

计数器不仅能用于对时钟脉冲计数,还可以用于分频,定时,产生节拍脉冲序列以及进行数字运算等,分为同步计数器和异步计数器,在同步计数器中,当时钟脉冲的输入时,触发器的翻转是同时发生的。而在异…

【SpinalHDL】1. Getting Started

1. Getting Started

1.1 SpinalHDL开发环境的搭建

开发环境的搭建参考SpinalHDL 开发环境搭建一步到位(图文版) - 极术社区 - 连接开发者与智能计算生态就可以了,so detail.

重点在于sbt切换为国内源,可以参考如下链接Windows上…

1.1 Verilog 教程

Verilog HDL(简称 Verilog )是一种硬件描述语言,用于数字电路的系统设计。可对算法级、门级、开关级等多种抽象设计层次进行建模。

Verilog 继承了 C 语言的多种操作符和结构,与另一种硬件描述语言 VHDL 相比,语法不是…

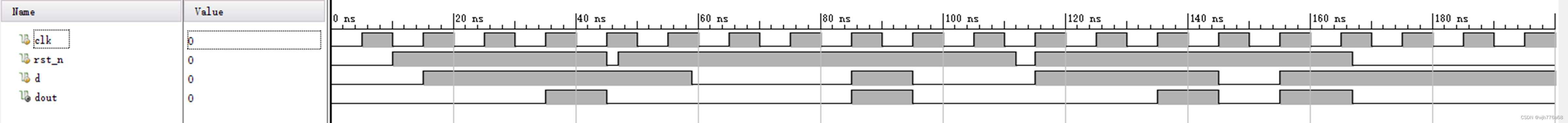

用verilog实现串行信号转8bit并行信号

串行信号转并行信号即为解串器(deserialize)。

输入信号有时钟信号clk,复位信号rst和串行数据输入信号din。

输出信号为8bit并行信号dout。

每经过8个时钟周期,便把收到的8个串行信号合成并行信号并输出,等下8个时钟…

异步FIFO设计的仿真与综合技术(6)

概述 本文主体翻译自C. E. Cummings and S. Design, “Simulation and Synthesis Techniques for Asynchronous FIFO Design 一文,添加了笔者的个人理解与注释,文中蓝色部分为笔者注或意译。前文链接:

异步FIFO设计的仿真与综合技术…

数字逻辑:第一次实验记录

修改pin文件,告诉电脑接口和程序里面的变量名是什么关系

修改源文件,注意case最后有endcase,always后面要有begin和end,数字要写成3b111这样,if语句不要用大括号。

FPGA纯verilog实现8路视频拼接显示,提供工程源码和技术支持

目录 1、前言版本更新说明免责声明 2、我已有的FPGA视频拼接叠加融合方案3、设计思路框架视频源选择OV5640摄像头配置及采集静态彩条视频拼接算法图像缓存视频输出 4、vivado工程详解5、工程移植说明vivado版本不一致处理FPGA型号不一致处理其他注意事项 6、上板调试验证并演示…

「Verilog学习笔记」优先编码器Ⅰ

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 分析 分析编码器的功能表: 当使能El1时,编码器工作:而当E10时,禁止编码器工作,此时不论8个输入端为何种状态&…

Circuits--Sequential Logic --Counters--Countslow

网址:https://hdlbits.01xz.net/wiki/Countslow

module top_module (input clk,input slowena,input reset,output [3:0] q);always(posedge clk)beginif(reset 1b1)q 4d0;else if(q 4d9 && slowena 1b1)q 4d0;else if(slowena 1b0)q q;elseq q 4…

Verilog Language--Vector--Vectorgates

网址:https://hdlbits.01xz.net/wiki/Vectorgates

module top_module( input [2:0] a,input [2:0] b,output [2:0] out_or_bitwise,output out_or_logical,

跨时钟域异步FIFO设计verilog(二)异步FIFO设计

三、设计要点解析

1、读空信号如何产生?写满信号如何产生? 读空信号:复位的时候,读指针和写指针相等,读空信号有效(这里所说的指针其实就是读地址、写地址) 当读指针赶上写指针的时候ÿ…

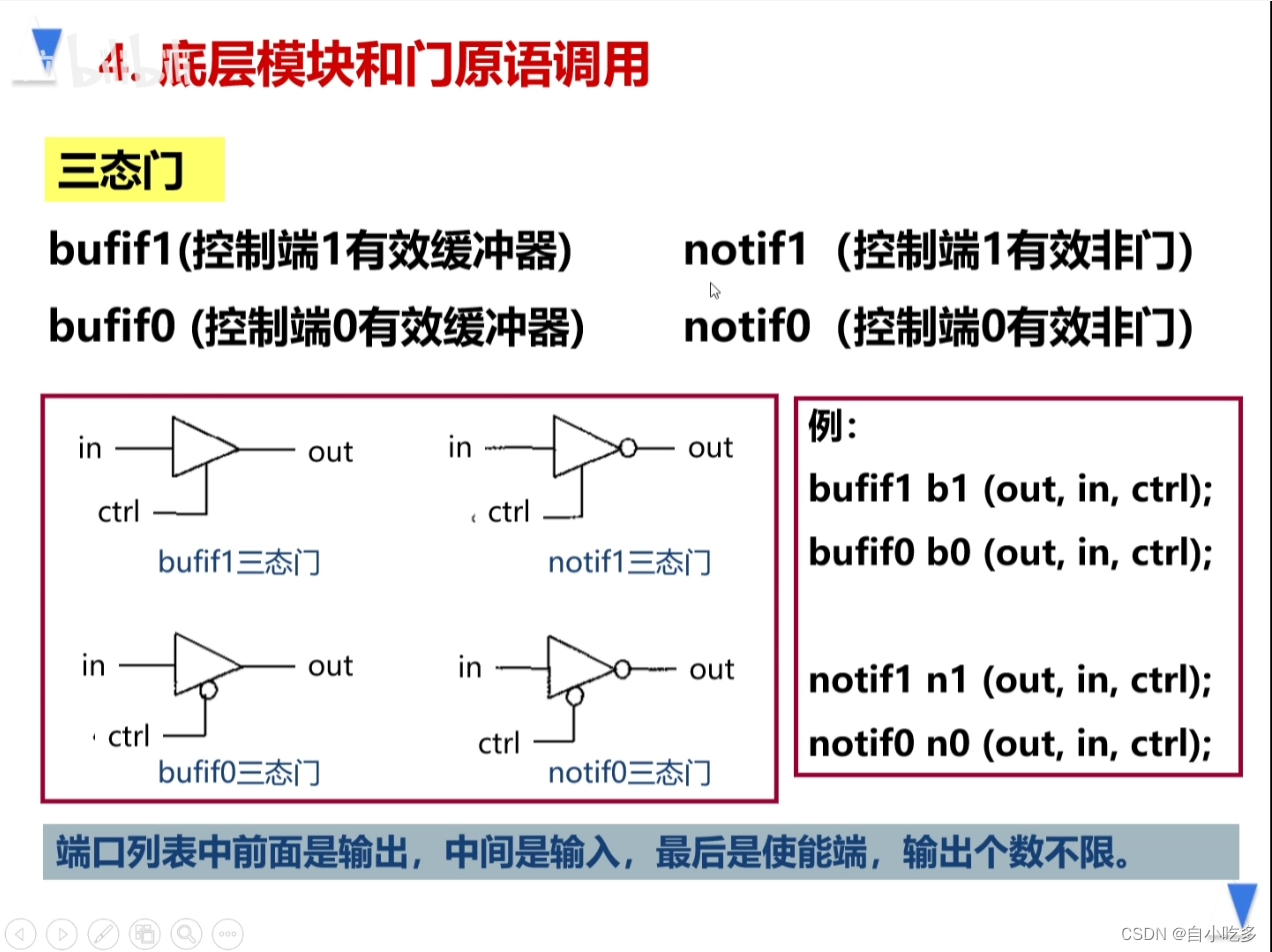

Verilog 入门(四)(门电平模型化)

文章目录 内置基本门多输入门简单示例 内置基本门

Verilog HDL 中提供下列内置基本门:

多输入门 and,nand,or,nor,xor,xnor 多输出门 buf,not 三态门上拉、下拉电阻MOS 开关双向开关

门级逻辑…

FPGA实现HDMI转LVDS视频输出,纯verilog代码驱动,提供4套工程源码和技术支持

目录 1、前言免责声明 2、目前我这里已有的图像处理方案3、本 LVDS 方案的特点4、详细设计方案设计原理框图视频源选择静态彩条IT6802解码芯片配置及采集ADV7611解码芯片配置及采集silicon9011解码芯片配置及采集纯verilog的HDMI 解码模块奇偶场分离并串转换LVDS驱动 5、vivado…

「Verilog学习笔记」状态机-非重叠的序列检测

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 根据题意 定义一个五位的中间变量lock 每次始终上升沿来临时 判断当前寄存器的低四位新数据是否等于10111 如果等于 则下一时刻lock应被清空 否则lock等于当前的lock的低四…

Verilog基础:时序调度中的竞争(一)

相关阅读

Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html?spm1001.2014.3001.5482 作为一个硬件描述语言,Verilog HDL常常需要使用语句描述并行执行的电路,但其实在仿真器的底层,这些并行执行的语句是有先后顺序…

「Verilog学习笔记」序列检测器(Moore型)

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 timescale 1ns/1nsmodule det_moore(input clk ,input rst_n ,input din ,output reg Y

); parameter S0 …

【Verilog】CRC校验码生成器原理及verilog实现

目录

一、CRC的基本原理 二、CRC生成步骤

2.1举个栗子

三、Verilog实现

四、参考资料

4.1 CRC在线计算器 一、CRC的基本原理

CRC :Cyclic Redundancy Check循环冗余校验码 将被处理的报文比特序列当做一个二进制多项式A(x)的系数,任意一个由二进制…

【Verilog】一文了解verilog基础语法

Verilog很简单,always..if..else走天下。

——鲁迅 目录

前言

一、Verilog HDL简介

二、Verilog模型

三、Verilog模块

四、Verilog数据类型

4.1常量

4.2参数型

4.3变量

4.3.1 wire型

4.3.2 reg型

4.3.3 memory型

五、运算符

六、赋值语句和块语句

6.…

verilog手撕代码7——固定优先级仲裁器和轮询仲裁器

文章目录 前言一、固定优先级仲裁器/Fixed Priority Arbiter1、case/if语句实现2、for循环语句实现参数化结构 二、轮询仲裁器/Round Robin Arbiter1、case语句实现2、for循环实现 前言

2023.5.16 天气炎热 最近实验推进一大步 一、固定优先级仲裁器/Fixed Priority Arbiter

…

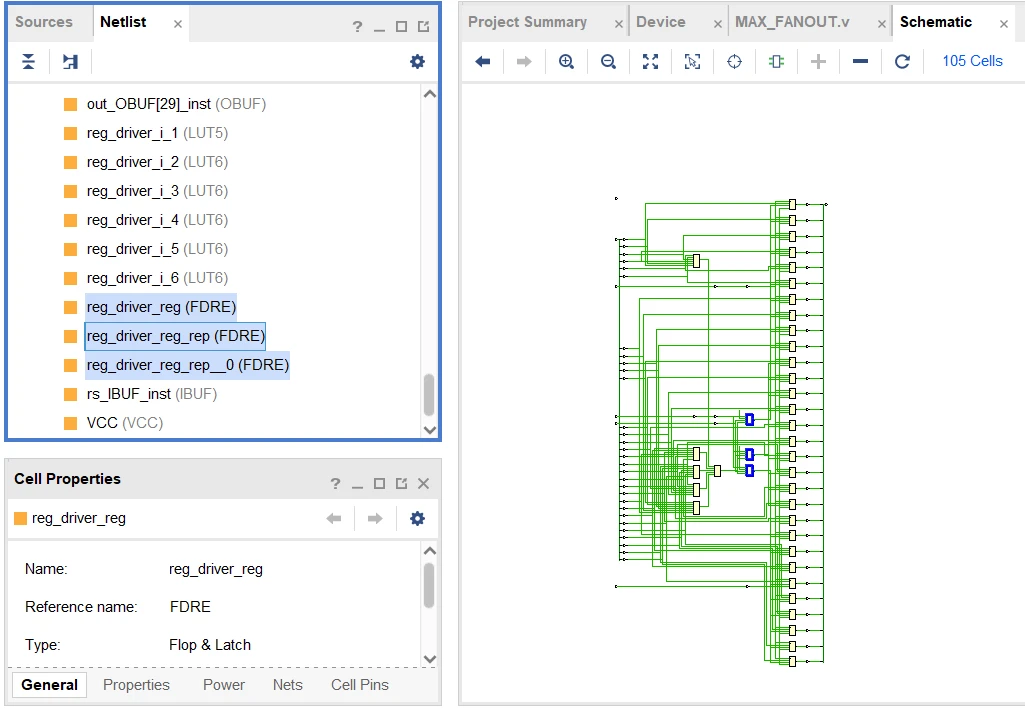

Vivado综合属性系列之六 MAX_FANOUT

目录

一、前言

二、MAX_FANOUT 2.1 工程代码 2.2 工程结果

一、前言 在时序违例的工程中,有一个很常见的原因:高扇出,此时就需要降低信号的扇出,可通过属性MAX_FANOUT来控制信号的扇出值ÿ…

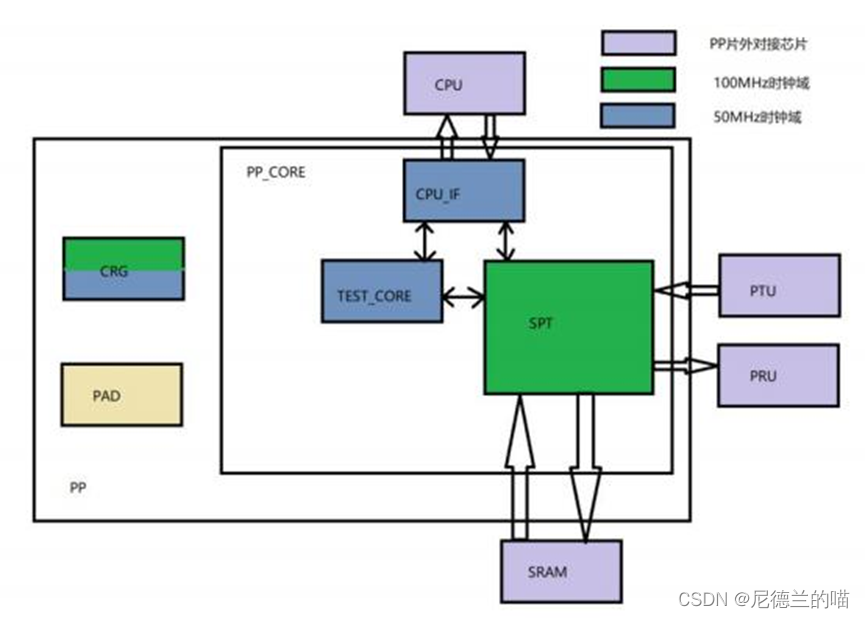

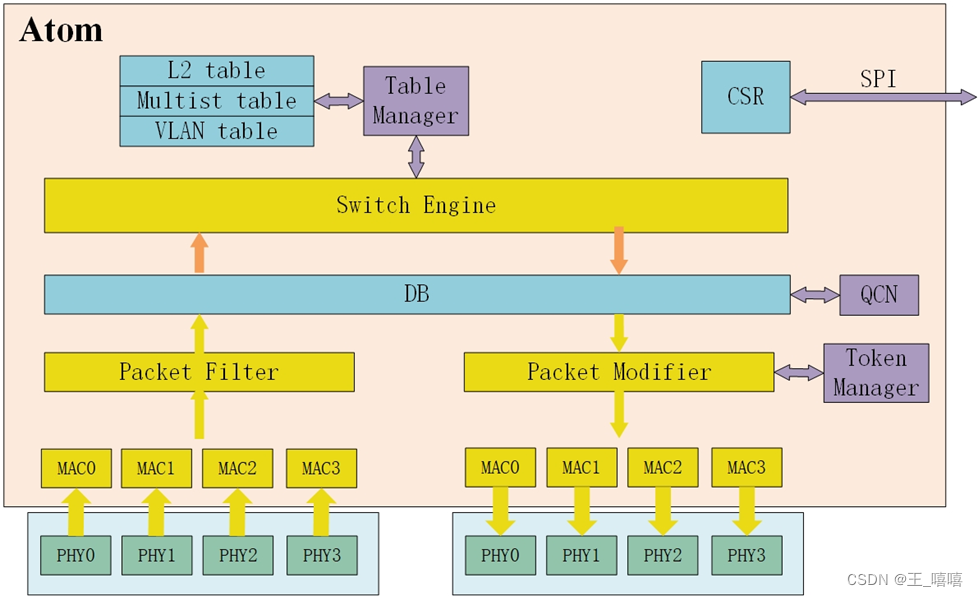

【HISI IC萌新虚拟项目】Package Process Unit模块整体方案·PART2

4.系统功能和主要技术指标论证 4.1芯片总体结构图 芯片总体结构框图如图2所示。 图 2 packet_process_unit 芯片结构框图 芯片内部主要电路包括 cpu_if 接口电路、sram 检测电路 test_core 以及 spt 包转发接口电 路。以下对主要部分分别进行简要介绍:

1.cpu_if 接口电路

该…

如何编写简单的testbench和运行仿真(三)——modelsim的一些操作技巧

这里写出的某些技巧或许不值一提。欢迎大家把自己知道的有用技巧分享在评论区,我会更新进本文,另外我也会把自己以后想到的一些技巧更新进来,故本文会不定期更新。

1、Modelsim显示信号名的简称

默认情况下modelsim的wave窗口会以全名显示信…

Verilog实现IIC协议读写EEPROM

在FPGA设计中,IIC协议是一个十分常见的协议,因为几乎所有的EEPROM都是用这个协议进行读写的,此外,一些特殊场合,也会用到此协议。这里我首先给出IIC协议的中文标准文档的下载链接(不要积分)&…

初学Verilog语言基础笔记整理(实例点灯代码分析)持续更新~

实例:点灯学习 一、Verilog语法学习

1. 参考文章 刚接触Verilog,作为一个硬件小白,只能尝试着去理解,文章未完…持续更新。 参考博客文章:

Verilog语言入门学习(1)Verilog语法【Verilog】一文…

Exams/2012 q1g

module top_module (input [4:1] x,output f

); assign f ~x[2]&~x[4] | ~x[1]&x[3] | x[2] & x[3] & x[4];

endmodule

FPGA开发基本流程详解

FPGA是一种可编程逻辑器件,与传统的硬连线电路不同,它具有高度的可编程性和灵活性。FPGA的设计方法包括硬件设计和软件设计两部分,硬件设计包括FPGA芯片电路、存储器、输入输出接口电路等等,软件设计则是HDL程序开发,以…

Vivado下阻塞赋值和非阻塞赋值的对比

Verilog 基础知识 中已经介绍过了阻塞赋值和非阻塞赋值的区别,下面通过一个在Vivado中的简单例子来直观的反映两者的不同。 首先给出设计源代码如下。

module block(a,b,c,clk,x);input x;input clk;output reg a,b,c;always(posedge clk)

begina x; //阻塞赋值…

Verilog笔记之booth乘法器

以3*7为例,首先写出乘数和被乘数的二进制表达式,分别为0011,0111;

其中,3是被乘数,7是乘数,将乘数的补码形式表示出来,为:1001

booth乘法器步骤:

1、初始化…

Vivado下时序逻辑模块的仿真

文章目录 D触发器两级D触发器带异步复位的D触发器带异步复位和同步置数的D触发器移位寄存器单口RAM伪双口RAM真双口RAM单口ROM 组合逻辑电路在逻辑功能上特点是任意时刻的输出仅仅取决于当前时刻的输入,与电路原来的状态无关。 时序逻辑在逻辑功能上的特点是任意时刻…

Verilog基础之四、乘法器实现

目录

一、前言

二、代码实现

2.1 工程代码

2.2 综合结果

2.3 仿真结果

三、参考 一、前言 本文介绍verilog实现乘法器,乘法的实现本质可以通过移位和加法实现,乘法的实现无需时序控制,用组合逻辑电路实现即可,因此即可用alw…

蜂鸣器电子琴 Verilog

蜂鸣器

电子琴 module beep

(CLK_50M,RST_N,KEY,BEEP

);input CLK_50M;

input RST_N;

input [7:0] KEY;output BEEP;//内部接口申明reg [19:0] time_cnt;

reg [19:0] time_cnt_n;

reg [15:0] freq;

reg beep_reg;

reg beep_reg_n;always(posedge CLK_50M or neged…

VPI step by step(1)

本文主要参考”The Verilog PLI Handbook(Second Edition)”, 权当读书笔记。主要针对VCS flow, 也许会穿插其他两大家工具的flow. 说在最前面

到今天为止,SV对C/Cpp的主要接口支持大多改用DPI, 也推荐使用DPI。或者直接使用UVM自带现成的DPI lib, 已经可以满足不少…

数码管动态扫描Verilog

数码管进阶

动态扫描 module SEG

(CLK_50M,RST_N,SEG_DATA,SEG_EN

); input CLK_50M;

input RST_N;output reg [5:0] SEG_EN;

output reg [7:0] SEG_DATA;reg [15:0] time_cnt;

reg [15:0] time_cnt_n;reg [2:0] led_cnt;

reg [2:0] led_cnt_n;parameter SET_T…

基于FPGA的交通灯设计

简易交通灯系统的设计与实现

最近期末了,听说很多人都在为数电大作业着急,分享一个自己做的交通灯,详细过程可以私聊我,也可以为你的设计出谋划策。其实课程之所以有这样一个要求,主要是想让大家能学以致用࿰…

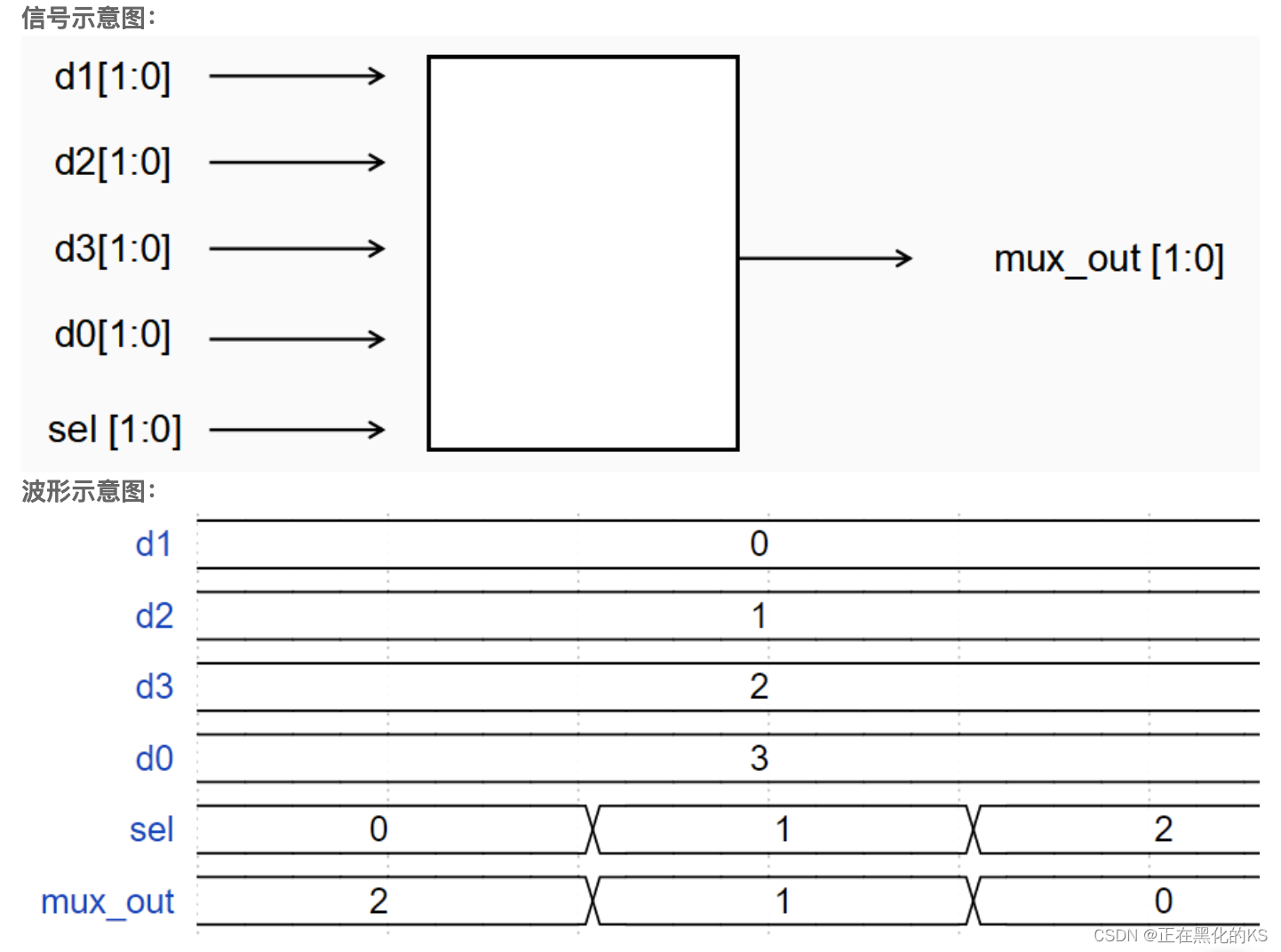

「Verilog学习笔记」四选一多路器

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 分析 通过波形示意图我们可以发现,当sel为0,1,2时,输出mux_out分别为d3,d2,d1,那么sel3…

用vhdl写testbench文件的简单方法

Vhdl -- 写Testbench

1 六进制计数器的代码

Library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity cnt6 is port (clr,en,clk :in std_logic; q :out std_logic_vector(2 downto 0) ); en…

「Verilog学习笔记」占空比50%的奇数分频

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 根据题意7分频,实际上是第一次电平变化经历了4个上升沿3个下降沿,第二次电平变化是4个下降沿3个上升沿,所以用两个计数器就行了。分别对…

基于FPGA的 TMDS 编码 及 HDMI 显示

目录

引言

TMDS 编码

原理简介

TMDS编码实现 HDMI差分数据串行

实现方法

源码

HDMI显示方法

思路

实现

工程结构

源代码分享

板级调试视频 引言

最近在开发板上倒腾了一下 TMDS 视频编码的原理以及实现。特在此做一个记录。文附 全部设计源码、MATLAB源码…

同步FIFO的verilog实现(2)——高位扩展法

一、前言 在之前的文章中,我们介绍了同步FIFO的verilog的一种实现方法:计数法。其核心在于:在同步FIFO中,我们可以很容易的使用计数来判断FIFO中还剩下多少可读的数据,从而可以判断空、满。 关于计数法实现同步FIFO的详…

Verilog基础:仿真时x信号的产生和x信号对于各运算符的特性

相关阅读

Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html?spm1001.2014.3001.5482 信号爆x也许是所有IC人的噩梦,满屏的红色波形常让人头疼不已,但x信号的产生原因却常常只有几种,只要遵循一定的代码规范&#…

HDLbits-Circuits(电路)-Combination Logic(组合逻辑)

目录

Arithmetic Circuits(算数电路)

1.Bcdadd4

Karnaugh Map to circuit(卡诺图到电路)

1.Kmap1

2.Kmap2

3.Kmap3

4.Kmap4

5.Exams/ece241 2013 q2 6.Exams/m2014 q3 7.Exams/m2012 q1g

8.Exams/ece241 2014 q3 Arithme…

FPGA纯verilog代码读写N25Q128A QSPI Flash 提供工程源码和技术支持

目录1、N25Q128A芯片解读2、N25Q128A读写时序3、整体设计思路架构4、verilog读写Flash驱动设计5、verilog读写Flash控制器设计6、FIFO缓存设计7、串口输出Flash读取数据8、vivado工程介绍9、上板调试验证并演示10、福利:工程源码获取1、N25Q128A芯片解读

N25Q128A的…

三人表决器Verilog

实战篇

三人表决器

外设

LED

功能概述设计说明

module LED

(LED0,LED1,LED2,LED3,LED4,LED5,LED6,LED7

);output LED0,LED1,LED2,LED3,LED4,LED5,LED6,LED7;assign LED01b1;

assign LED11b0;

assign LED21b0;

assign LED31b0;

assign LED41b1;

assign LED51b0;

assign LED…

FPGA纯verilog代码实现图像对数变换,提供工程源码和技术支持

目录1、图像对数变换理论2、log系数的matlab生成3、FPGA实现图像对数变换4、vivado与matlab联合仿真5、vivado工程介绍6、上板调试验证并演示7、福利:工程代码的获取1、图像对数变换理论

对数变换可以将图像的低灰度值部分扩展,显示出低灰度部分更多的细…

Verilog中的 条件语句\多路分支语句\循环语句

Verilog中的条件语句\多分支语句\循环语句 文章目录 Verilog中的条件语句\多分支语句\循环语句一、背景二、if-else2.1 标准结构2.2 例子 三、case-endcase3.1 标准结构3.2 例子3.2.1 三路选择器的case部分,如下:3.2.2 casez的四路选择器,如下…

HDLBits-Verilog学习记录 | Verilog Language-Basics(1)

文章目录 3.Simple wire4.Four wires5.inverter | Notgate6. And gate7.Nor gate8.Xnorgate 3.Simple wire

problem:Create a module with one input and one output that behaves like a wire.

module top_module( input in, output out );assign out in;endmodule4.Four w…

【FPGA】FPGA实现IIC协议读写EEPROM(三) ----- 汇总篇

IIC协议读写EEPROM一、功能分析/模块划分二、状态转移图1、EEPROM读写控制状态转移图2、IIC接口驱动状态转移图三、工程代码实现1、顶层模块2、EEPROM读写控制模块3、IIC接口驱动模块4、参数配置5、其他模块四、仿真测试五、上板验证写在前面 FPGA实现IIC协议读写EEPROM相关文章…

HDLBits练习答案(持续更新)

HDLBits练习答案1.Getting Started2. Verilog Language2.3 Modules:Hierarchy2.3.5 Modules and vertors2.3.6 Adder 12.3.7 Adder 22.3.8 Carry-select adder2.3.9 Adder-subrtactor2.4 Procedures2.4.1 Always block12.4.2 Always block22.4.4 If statement2.4.5 If statemen…

深入浅出学Verilog--基础语法

1、简介 Verilog的语法和C语言非常类似,相对来说还是非常好学的。和C语言一样,Verilog语句也是由一连串的令牌(Token)组成。1个令牌必须由1个或1个以上的字符(character)组成,令牌可以是&#x…

【Verilog 教程】5.1Verilog 模块与端口

关键词:模块,端口,双向端口,PAD 结构建模方式有 3 类描述语句: Gate(门级)例化语句,UDP (用户定义原语)例化语句和 module (模块) 例化语句。本次主要讲述使用最多的模块级例化语句。…

FPGA开发软件(vivado + modelsim)环境搭建(附详细步骤)

本文详细介绍了vivado软件和modelsim软件的安装,以及vivado中配置modelsim仿真设置,每一步都加文字说明和图片。一、软件安装包下载1、vivado vivado版本很多,目前最新的已更新到vivado2022.2,版本越高,安装包越大&…

【FPGA】Verilog:组合电路设计 | 三输入 | 多数表决器

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载的示例:表决器(三人表决器)。 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片 配置方式:USB-JTAG/SPI Flash 高达100MHz 的内部…

verilog常用系统任务和函数

在FPGA开发中编写仿真测试激励文件(testbench),经常会用到verilog的系统函数,使用系统函数非常方便,本文总结了常用的系统函数,并提供了说明和使用示例。一、文件操作1、打开文件$fopen和关闭文件$fclosein…

【Verilog】不用IP,你能写出异步FIFO的verilog代码吗?

前集回顾:

【Verilog】同步FIFO原理及verilog实现 目录

一、方案设计 二、Verilog代码:

三、仿真 一、方案设计 异步FIFO使用完全独立的读写时钟,empty由读时钟产生,full由写时钟产生,两者关系完全异步,…

Quartus Ⅱ中遇到的问题

记录Quartus中遇到的报错

一、Failed to launch MegaWizard Plug-In Manager

报错:Failed to launch MegaWizard Plug-In Manager. PLL IntelFPGA IP v18.1 could not be found in the specified librarypaths.

原因:编译后无法再打开IP核查看了&…

基于FPGA的 SPI通信 设计(1)

引言

低速通信目前搞过 UART串口通信、IIC通信。其实 SPI 也算是中低速(有时也可以用作高速通信)串行通信的范畴,但是一直还没真正实现过,所以此系列就 SPI的协议以及FPGA设计作几篇博客记录。欢迎订阅关注~ SPI 标准协议 x1模式…

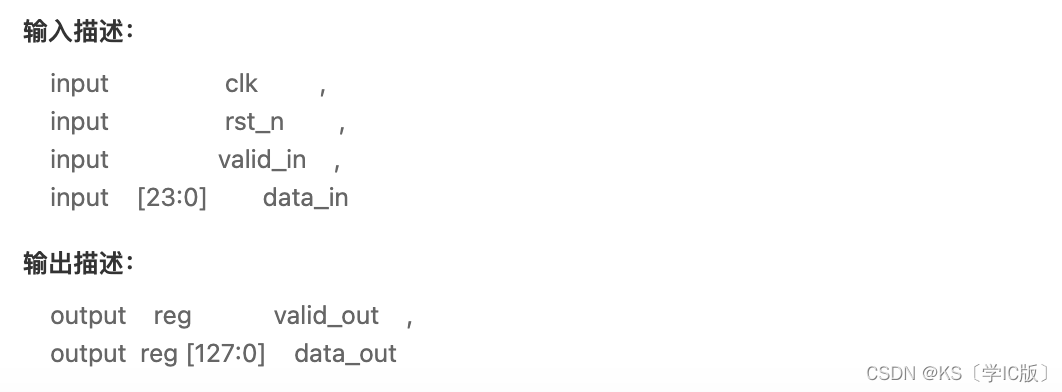

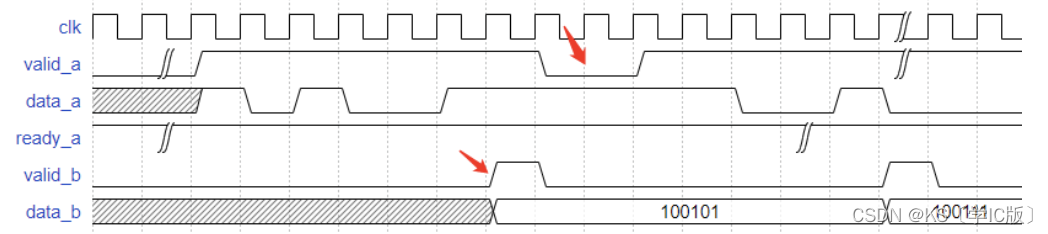

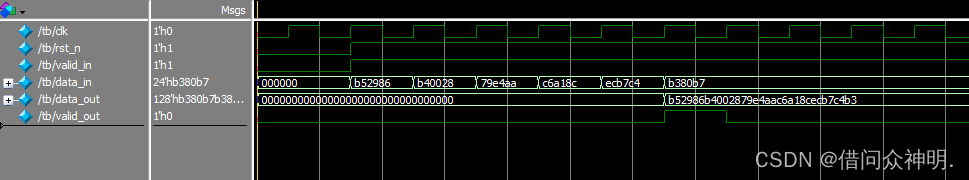

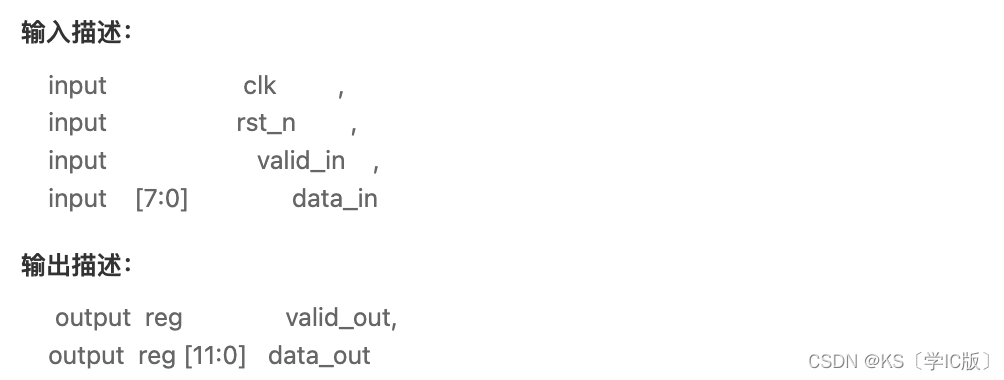

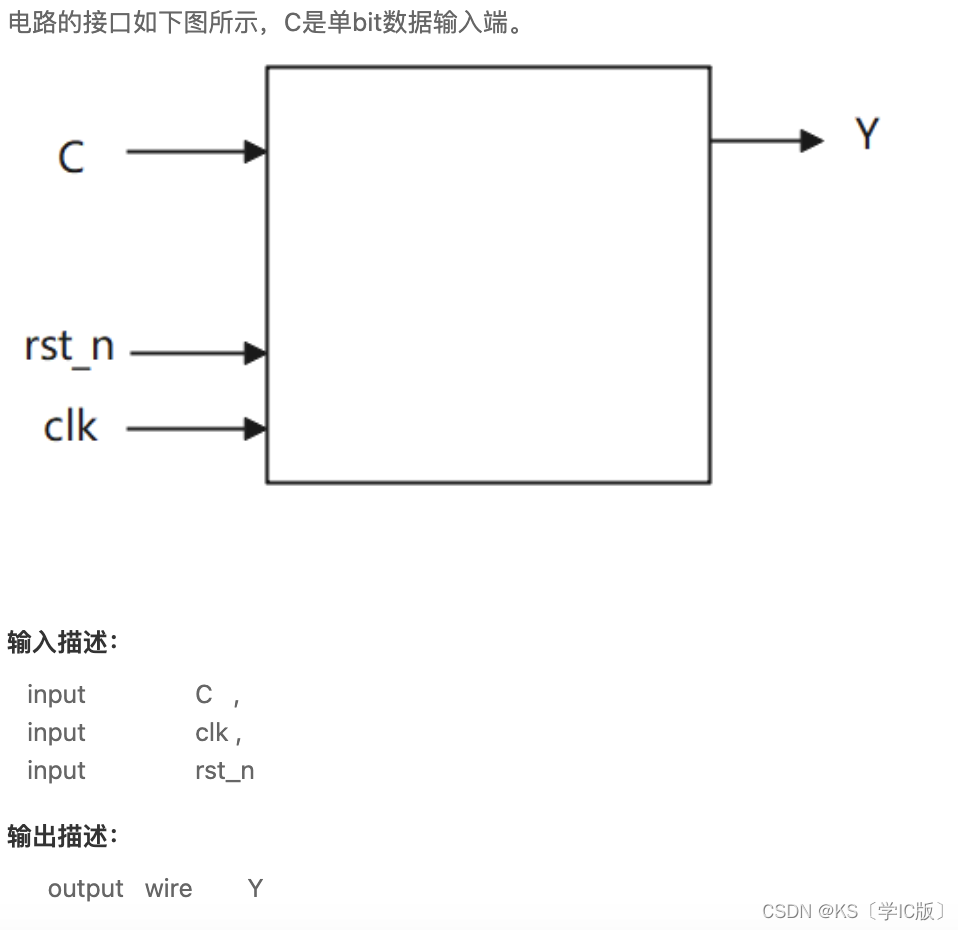

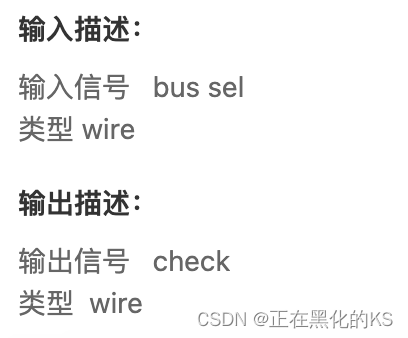

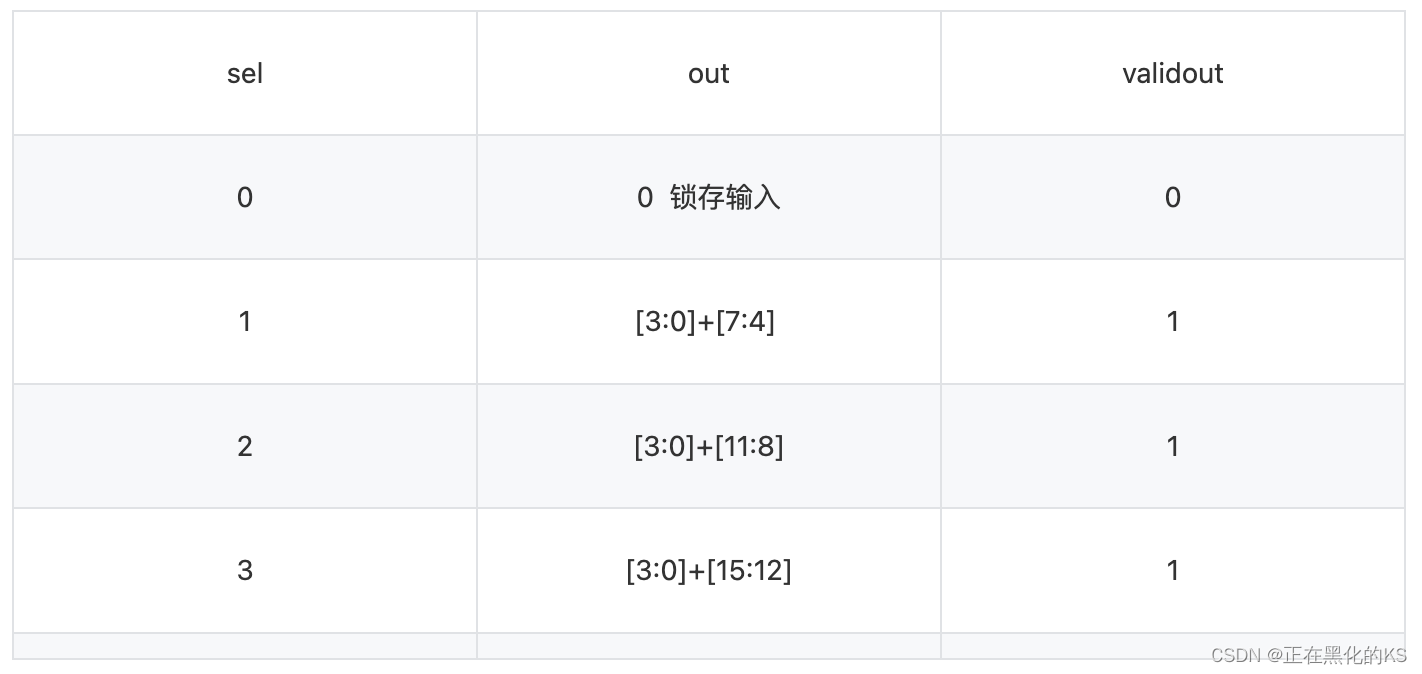

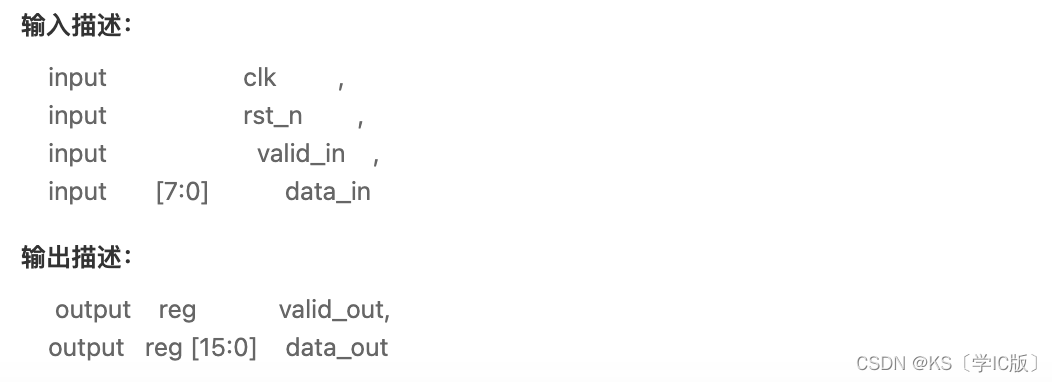

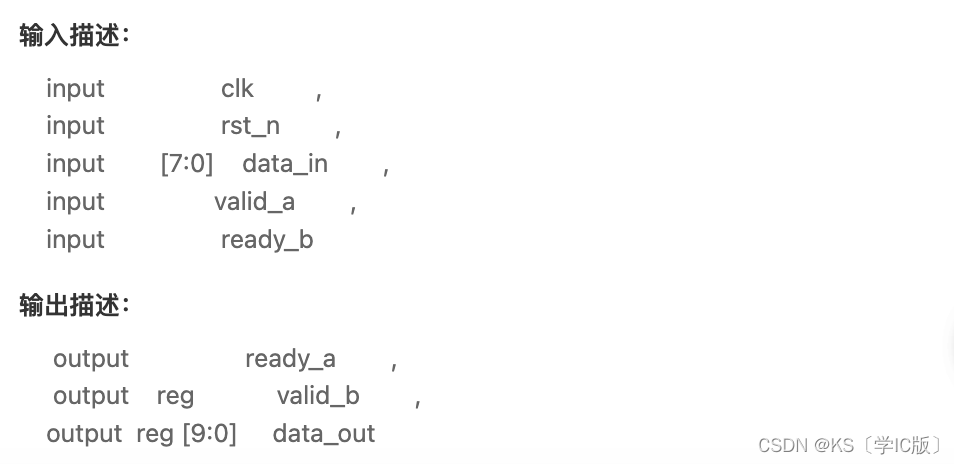

24位数据转128位

实现24bit数据输入转换为128bit数据输出。其中,先到的数据应置于输出的高bit位。电路的接口如下图所示。valid_in用来指示数据输入data_in的有效性,valid_out用来指示数据输出data_out的有效性;clk是时钟信号;rst_n是异步复位信号…

数据累加输出---verilog

文章目录介绍思路分析代码实现介绍

本题目来源为牛客网中在线编程>verilog模块,要求实现串行输入数据累加输出,输入端输入8bit数据,每当模块接收到4个输入数据后,输出端输出4个接收到数据的累加结果。输入端和输出端与上下游的…

【牛客网】Verilog快速入门-基础语法(1)

⭐作者: 桐桐花❀ ⭐个人主页:桐桐花的博客_CSDN博客-python,Verilog,数字IC领域博主 ⭐系列专栏:Verilog刷题_桐桐花的博客-CSDN博客 ⭐推荐刷题神器:牛客网 - Verilog刷题模块 Verilog快速入门-基础语法篇(1&a…

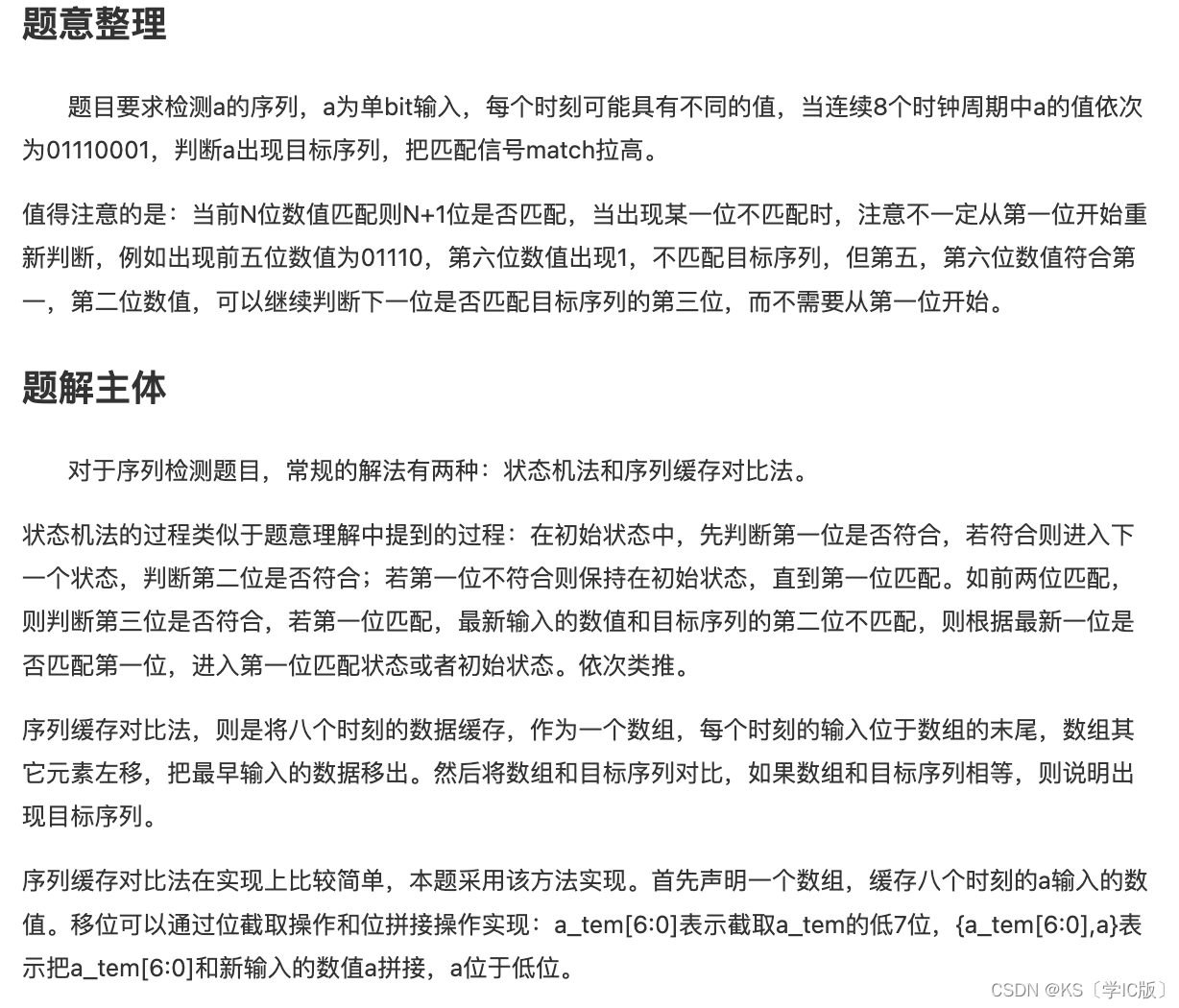

verilog实现序列检测(状态机和移位寄存器实现)

前言

用Verilog描述一个可综合的序列检测器用于检测输入数据码流中的特定序列。本文介绍了使用状态机来直接描述和采用移位寄存器的方式进行检测的两种方法。同时,也给出了tb文件和仿真波形图。

状态机方法

本文实现了对序列“1010”的检测,第一种方法…

数字ic设计——AMBA总线(2)AHB

典型的AMBA系统:

一个以 AMBA 架构的 SOC,一般来说包含了

AHB(high-performance 的 system bus ): 负责连接例如 ARM 之类的 embedded processor 与 DMA controller,on-chip memory 和其他 interface&…

数字ic设计——SPI

SPI总线概念 SPI ( Serial Peripheral Interface,串行外围设备接口)是一种同步、全双工、主从式,高速接口(UART是异步)。 来自主机或 从机 的数据在时钟上升沿或下降沿同步。主机和从机可以同时传输数据。 串行外设接…

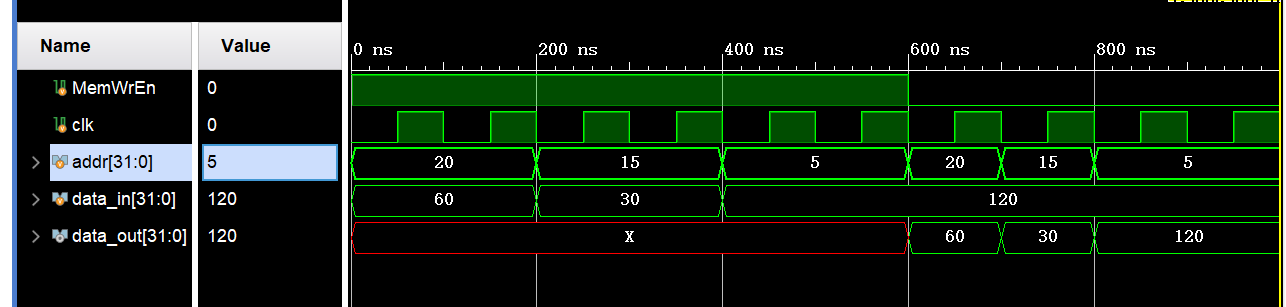

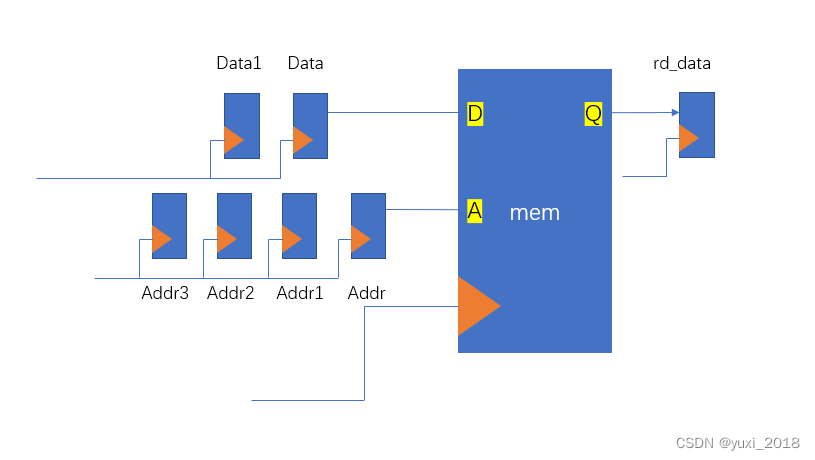

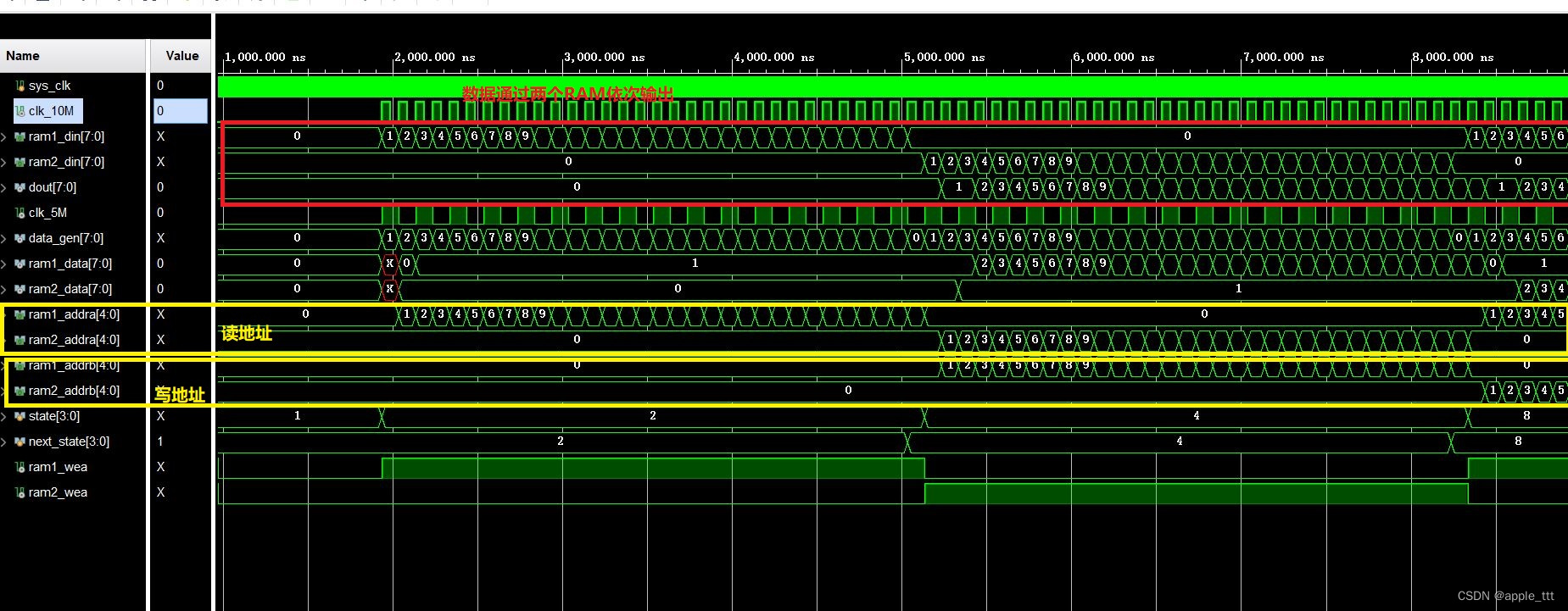

【28】Verilog进阶 - RAM的实现

VL53 单端口RAM

1 思路 简简单单,读取存储器单元值操作即可 2 功能猜想版 说明: 下面注释就是我对模块端口信号 自己猜测的理解。 因为题目并没有说清楚,甚至连参考波形都没有给出。 唉,这就完全是让人猜测呢,如果一点学术背景的人来刷题,指定不容易!! 好在,我有较为…

数字ic设计——UART

UART定义 UART 的全称是通用异步收发器(Universal Asynchronous Receiver/Transmitter),是实现设备之间低速数据通信的标准协议。 是一种通用的串行、异步通信总线。 该总线有两条数据线,可以实现全双工的发送和接收在嵌入式系统中…

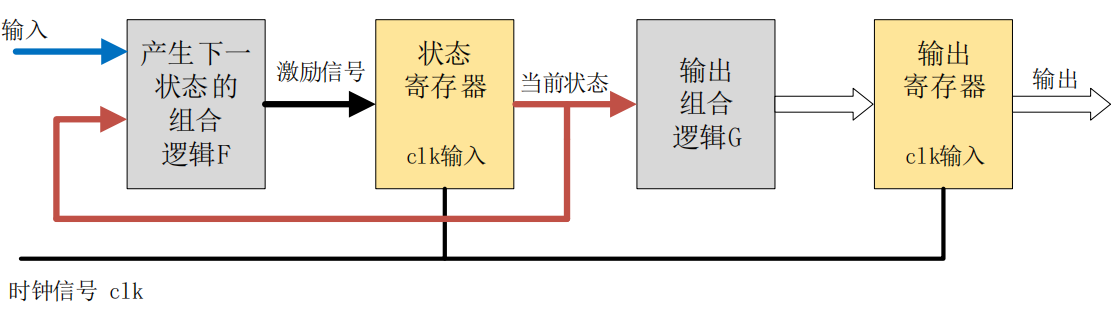

《计算机组成与CPU设计实验》5有限状态机的Verilog HDL描述(Finite State Machine,FSM)

多数控制逻辑都可以用有限状态机描述

状态机

状态机是组合逻辑和时序逻辑的特殊组合

时序逻辑用于存储状态组合逻辑用于产生次态和产生输出

状态的数量是有限的,故称为有限状态机(Finite State Machine,简称为FSM) 状态机分类 …

Verilog入门教程与实例分享

本文目录前言一、Verilog入门教程1.基础语法2.数值表示3.数据类型4.表达式5.编译指令6.过程结构7.过程赋值8.语句块9.连续赋值语句10.延时语句11.时序控制12.条件语句13.多路分支语句14.循环语句15.过程连续赋值16.数值转换二、Verilog实例分享1.计算数据位数2.多次判断3.循环计…

用verilog实现去抖动电路(状态机实现)

题目:用Verilog实现按键抖动消除电路,抖动小于20ms,输入时钟10MHz。

按键在按下的时候会有抖动特点,如果不加以处理,可能会被识别为多次按下,所以要设计去抖动电路。

去抖动电路的核心思想就是通过计数器…

用verilog实现异步复位、同步释放电路

相关重要概念:建立时间,保持时间;同步时序,异步时序;亚稳态;

时序电路里面需要复位,异步复位相比于同步复位最大的优点就是可以节约资源。

但是异步复位在上升沿时如果同时遇到时钟的上升沿&a…

用verilog实现加法器

用verilog实现加法器 加法器是组合逻辑电路中的常见器件,了解其结构很有必要。

解决加法问题的根本是解决进位问题,解决进位问题的根本是理解加法竖式。比如计算二进制加法 1001(reg[3:0] in1) 1101(reg[3:0] in2&am…

通过状态机实现序列检测

如何实现对某一序列的检测?当序列中出现‘1101’时,输出‘1’,其余情况输出‘0’。

通过有限状态机可以实现此功能。

FSM(finite-state machine)是有限状态机,是指状态数为有限个的状态机。

本题目中的待…

Verilog中$timeformat的用法

Verilog中$timeformat的用法 更新历史 20200807: 首次发布 语法

$timeformat的语法如下:

$timeformat(units_number, precision_number, suffix_string, minimum_field_wdith);其中:

units_number 是 0 到-15 之间的整数值,表示…

【Verilog】状态机嵌套实现层次结构化设计

目的:

1.运用主状态机与子状态机产生层次化的逻辑设计; 2.在结构化设计中灵活使用任务(task)结构。 我们都知道如何使用状态机。实际上,单个有限状态机控制整个逻辑电路的运转在实际设计中是不多见,往往是…

【Verilog】同步FIFO原理及verilog实现(参数化)

旨在学习理解,项目中还是用成熟IP靠谱~ 目录

一、FIFO原理

二、同步FIFO设计

2.1 位宽和深度

2.2 空、满标志

2.3 FIFO计数

2.4 ram模型

2.5 读/写操作

三、verilog代码

四、仿真验证

后记 一、FIFO原理

FIFO( First Input First Output)是…

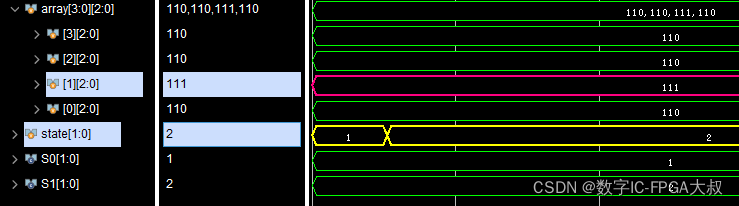

【Verilog】常见bug之for循环

Debug系列文章,想起哪个坑就把它埋了~

本文分享一个for循环的坑,见过了就别再踩了 在Verilog中,我们一般使用for语句进行循环操作。

假设场景: 某项目中,前面代码用到了一个二维数组array[3:0][2:0],如果array[i] 3…

「Verilog学习笔记」非整数倍数据位宽转换8to12

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 要实现8bit数据至12bit数据的位宽转换,必须要用寄存器将先到达的数据进行缓存。8bit数据至12bit数据,相当于1.5个输入数据拼接成一个输出数据&#…

【Verilog】随机数产生电路

1、伪随机序列 如果一个序列,一方面它是可以预先确定的,并且是可以重复地生产和复制的;一方面它又具有某种随机序列的随机特性(即统计特性),我们便称这种序列为伪随机序列。 伪随机序列又称为伪随机码&…

Verilog Tutorial(7)If语句和Case语句

写在前面在自己准备写verilog教程之前,参考了许多资料----FPGA Tutorial网站的这套verilog教程即是其一。这套教程写得不错,只是没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。这是网站原文:h…

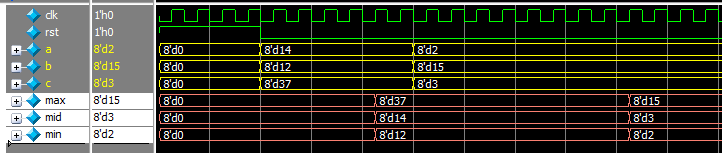

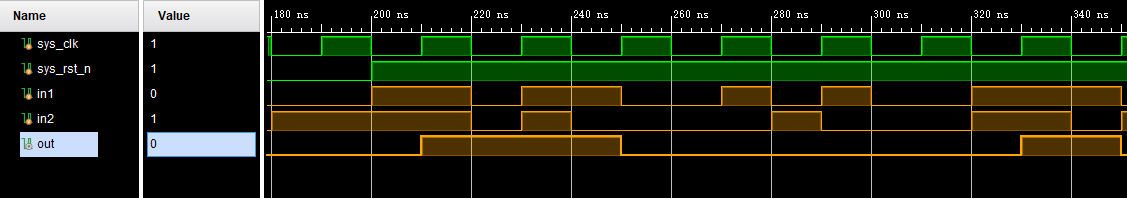

【Verilog】通过任务(task)完成3个8bit数据的冒泡排序

题目:

设计一个模块,通过任务完成3个8位2进制输入数据的冒泡排序。要求:时钟触发任务的执行,每个时钟周期完成一次数据交换的操作。 Verilog代码:

module sort(input sys_clk,input sys_rst,input [7:0] a,in…

Verilog常用的系统函数和任务(不定期更新)

我们在开发FPGA的过程中,特别是编写testbench时,经常会用到Verilog的系统函数,在查看Xilinx官方testbench或者大神写的testbench时,也会看到各种各样的系统函数,系统函数的特点就是前面带有$符号。灵活使用系统函数可以…

轻量化Verilog开发环境搭建

轻量化Verilog学习环境搭建

本文记录基于vscode、iverilog搭建轻量化Verilog学习环境的方法。 ref: VSCode Verilog工具链、linux下搭建轻量易用的verilog仿真环境

环境搭建

(1)安装iverilog,这是一个轻量化的开源verilog编译器࿰…

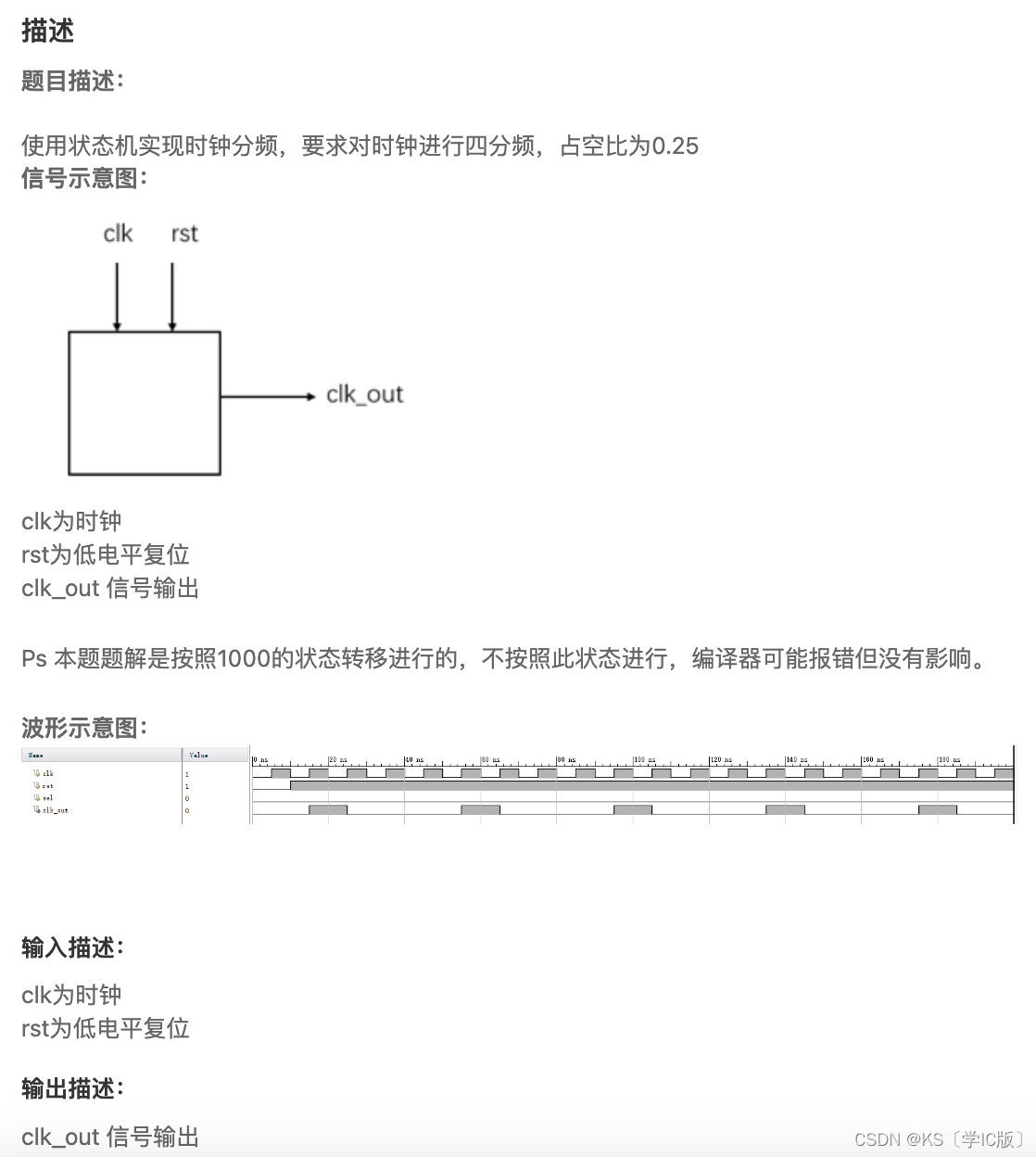

【牛客】VL65 状态机与时钟分频

描述

题目描述:

使用状态机实现时钟分频,要求对时钟进行四分频,占空比为0.25

信号示意图: clk为时钟 rst为低电平复位 clk_out 信号输出 Ps 本题题解是按照1000的状态转移进行的,不按照此状态进行,编译器…

SOC设计:关于reset的细节

有如下几个信号

1、时钟:clk_top

2、总的reset信号:rstn_top

3、scan的reset信号:scan_rstn

4、软件复位信号:rstn_soft_sub

5、scan模式信号:scan_mode

6、reset bypass 信号:scan_rstn_sel

功能&a…

UART接口的FPGA实现(二)——UART接口的Verilog代码实现以及仿真测试

废话不多说,先上源代码链接和testbench的链接,推荐使用UE查看源代码,UE中的VHDL语法、Verilog语法和SystemVerilog语法高亮文件的下载链接在这里。上篇的最后给出了本篇所附代码的uart通信模型的工作过程。本篇的主要内容在源代码里ÿ…

如何编写简单的testbench和运行仿真(二)——简单的testbench和仿真脚本

废话不多说,先上本文中所使用的testbench和仿真脚本的源代码链接。我们可以在我们的工程目录下建立一个src文件夹,用于存放待测设计的所有代码,另外再建立一个sim文件夹,用于存放testbench和仿真脚本。

一、简单的testbench的编写…

如何编写简单的testbench和运行仿真(一)——modelsim的命令

作为FPGA工程师,编写testbench是我们必须要学会的技能,一个成熟的testbench要包含验证方法学的理论和相关技术,这里只介绍最最简单的testbench,也就是通常说的把代码“跑起来”,成熟的testbench留在我后面写的UVM方法学…

计算机组成原理——单周期CPU

单周期CPU项目代码实验原理MIPS指令rom.coe文件代码顶层模块SingleCycleCPUdisplay外围模块PCinstructionMemoryAlu模块DataMemoryControlUnit旧的xdc功能仿真tb上板验证思考项目代码

vivado版本为2022.2 链接: CSDN资源:https://download.csdn.net/download/m0_46…

System Verilog-数据类型

System Verilog数据类型分为两大类,一类是变量(variable),一类是网线(net)。这两种类型在赋值和存储值上有所区别

net一般只用于assign连续赋值,部分net类型可以有多个驱动(driver&…

【IC萌新虚拟项目】spt_core模块基于dc的综合环境搭建与面积时序优化

关于整个虚拟项目,请参考: 【IC萌新虚拟项目】Package Process Unit项目全流程目录_尼德兰的喵的博客-CSDN博客 前言

当验证的同学正在疯狂写测试点,补充测试用例各种找茬找bug时候,设计的同学也要进入到跑综合修时序优化面积的阶段了。

还是老样子,关于芯片综合的知识就…

verilog学习笔记1——verilog延时语句

文章目录 前言一、延时语句分类1、阻塞赋值左侧延时2、阻塞赋值右侧延时3、非阻塞赋值左侧延时4、非阻塞赋值右侧延时 二、比较及举例说明1、阻塞右侧延时和非阻塞右侧延时的区别2、举例 前言

2023.8.10 一、延时语句分类

1、阻塞赋值左侧延时

在10ns后,把10ns时…

[HDLBits] Exams/2012 q1g

Consider the function f shown in the Karnaugh map below. Implement this function.

(The original exam question asked for simplified SOP and POS forms of the function.) //

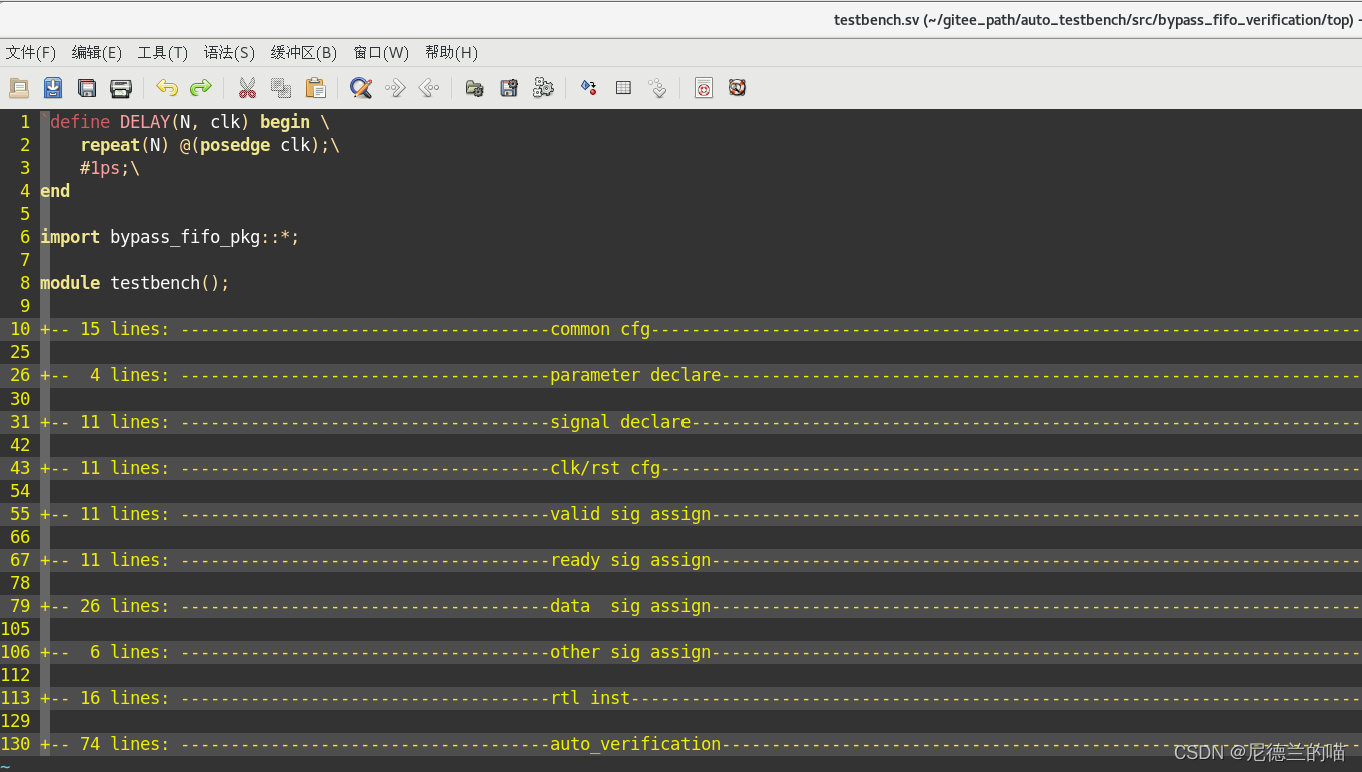

【芯片前端】auto_testbench的大版本升级——加入简单预期与自动比对

前言

前文提要:

【芯片前端】一键生成简易版本定向RTL验证环境的脚本——auto_verification_rtl脚本_尼德兰的喵的博客-CSDN博客

【芯片前端】可能是定向验证的巅峰之作——auto_testbench_autotestbench_尼德兰的喵的博客-CSDN博客

工具路径:

auto…

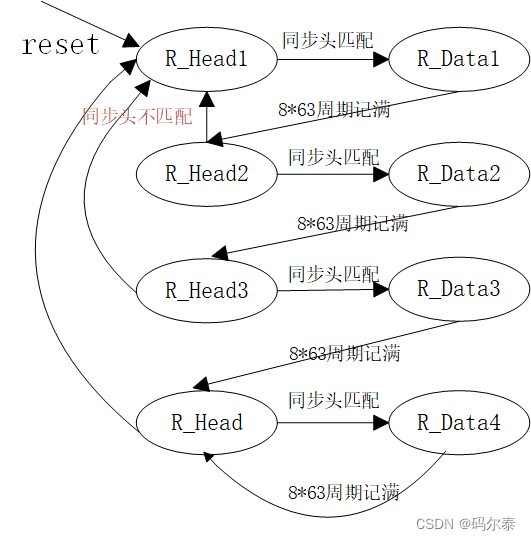

帧结构的串行数据接收器——Verilog实现

用Verilog 实现一个帧结构的串行数据接收器;

串行数据输入为:NRZ数据加位时钟(BCL)格式,高位在前 帧结构为:8位构成一个字,64字构成一个帧。每帧的第一个字为同步字。同步字图案存储在可由CPU读…

FPGA | Verilog仿真VHDL文件

当VHDL模块中有Generic块时,应该怎么例化?

VHDL模块代码

entity GenericExample isgeneric (DATA_WIDTH : positive : 8; -- 泛型参数:数据宽度ENABLE_FEATURE : boolean : true -- 泛型参数:是否启用特定功能);Port ( clk : …

基于FPGA的图像累积直方图verilog实现,包含tb测试文件和MATLAB辅助验证

目录

1.算法运行效果图预览

2.算法运行软件版本

3.部分核心程序

4.算法理论概述

5.算法完整程序工程 1.算法运行效果图预览 2.算法运行软件版本

Vivado2019.2

matlab2022a

3.部分核心程序

timescale 1ns / 1ps

//

// Company:

// Engineer:

// // Design Name:

// …

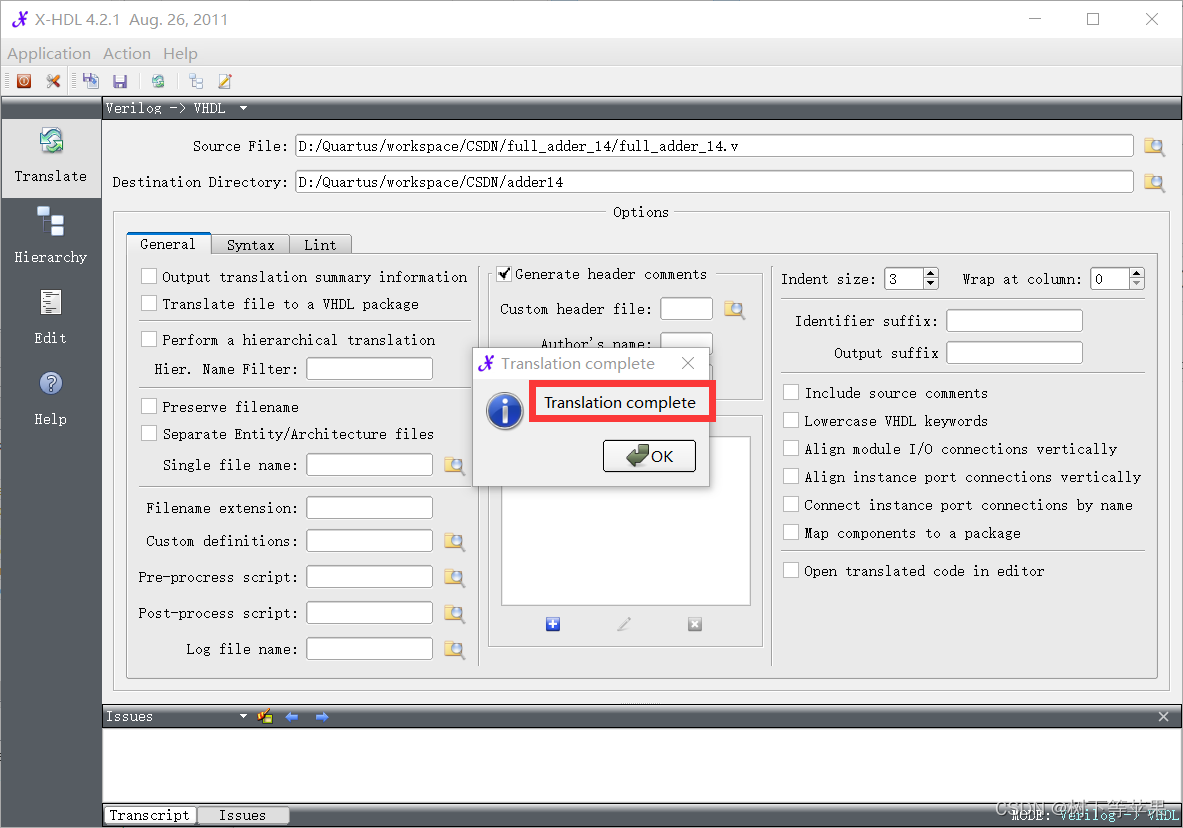

Verilog与VHDL代码转换工具X-HDL的安装、使用教程(详细)以及报错:Translation error的解决办法

一、安装 1、获取安装包: 链接:https://pan.baidu.com/s/12CuBeF2NNCnjLpAn6hpL6A 提取码:zwfz 2、解压压缩包,运行X-HDL-4.2.1-Setup.exe。 (1)弹出以下对话框,根据使用语言选择(没…

questasim的傻瓜式安装与仿真教程

一、安装 1、下载软件 链接:https://pan.baidu.com/s/1S05AnO_w-wy6RsAj_kdUXg 提取码:p2nt 2、根据电脑类型是32位还是64位,解压不同安装包。 解压得:

2、运行.exe文件,出现: 问题及解决办法ÿ…

Verilog HDL Conditional Statement error at xxx.v(8): cannot match operand(s) in the condition to the

一、问题描述 在学习Verilog的过程中,使用Verilog进行状态机设计,验证书中的代码时,出现以下错误。

//FSM.v 代码

module FSM(clk,clr,out,start,step2,step3);

input clk,clr,start,step2,step3;

output[2:0] out;reg[2:0] out;

reg[1:0] s…

资深IC工程师的快速学习指南《Verilog语言知识学习快速基础学习》

Verilog语言是一种硬件描述语言(HDL),广泛用于数字集成电路(IC)设计和硬件描述。对于IC行业的初学者来说,掌握Verilog语言是非常重要的,因为它是设计和仿真IC电路的基础。之前也分享过很多Veril…

Verilog入门设计(三)——组合电路和逻辑电路的仿真

数字电路仿真一、测试平台(Test Bench)1、测试程序一般结构2、激励信号产生方式举例2.1 initial语句产生激励信号2.2 always语句产生激励信号二、组合电路的仿真1、8位乘法器的仿真2、8位加法器的仿真3、2选1数据选择器的仿真三、时序电路的仿真8位计数器…

【Verilog】testbench仿真对文本数据的读取和写入

在需要进行数据对比的情况下,使用仿真波形来对比查看是比较费劲的,可以将仿真数据写入文本,然后使用文本比较软件(如beyond compare)来进行数据对比验证。 这里介绍一种方式。 实验内容:从文件1(…

移动FPGA使用Verilog图像处理verilator模拟和ice40执行

概述

在verilog中实现简单的图像处理操作。 该项目围绕一个中央图像处理模块 image_processing.v 展开,该模块可以包含在使用 verilator 的模拟环境中,也可以包含在 ice40 Ultraplus fpga 的 top.v 中。

因为它针对的是低端 fpga 设备(无论…

Vivado下组合逻辑模块的仿真

文章目录 与门或门非门异或门同或门比较器半加器全加器乘法器数据选择器3-8 译码器三态门 组合逻辑电路的特点是任意时刻的输出仅仅取决于输入信号,输入信号变化,输出立即变化,其变化不依赖于时钟。 本文中的例子中模块名都是gate,…

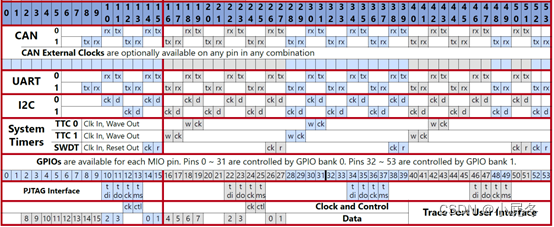

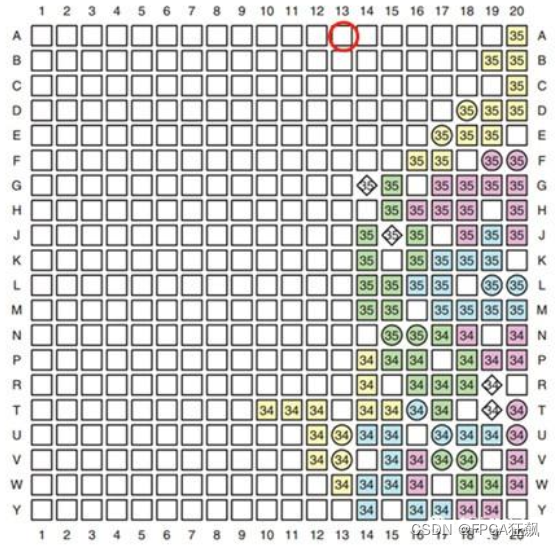

7Z010 引脚功能详解

本文针对7Z010芯片,详细讲解硬件设计需要注意的技术点,可以作为设计和检查时候的参考文件。问了方便实用,按照Bank顺序排列,包含配置Bank、HR Bank、HP Bank、GTX Bank、供电引脚等。

参考文档包括:

ds187-XC7Z010-X…

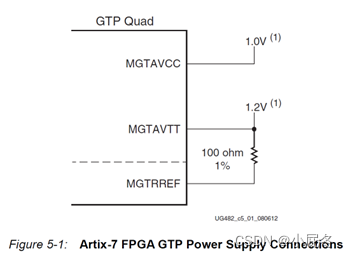

7A50T 引脚功能详解

本文针对7A50T芯片,详细讲解硬件设计需要注意的技术点,可以作为设计和检查时候的参考文件。问了方便实用,按照Bank顺序排列,包含配置Bank、HR Bank、HP Bank、GTP Bank、供电引脚等。

参考文档包括:

ds181_Artix_7_D…

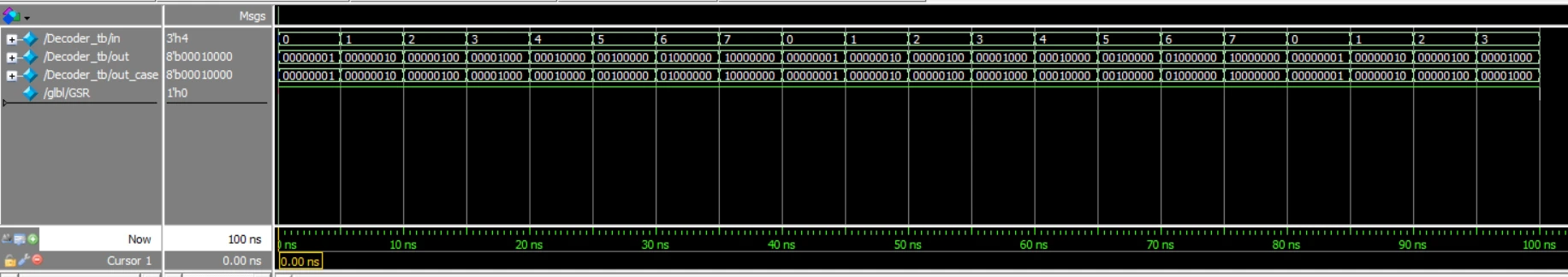

Verilog基础之七、译码器实现

目录

一、前言

二、工程实现

2.1 工程代码

2.2 仿真结果

2.3 参考 一、前言 译码器的实现为编码器的逆过程,以3-8译码器为例,真值表如下。 二、工程实现 实现同时使用for循环和case两种方式。

2.1 工程代码

module Decoder(in,out,out_case )…

【FPGA开发】Verilog 基础

写在前面:本章将对 Verilog 进行简要介绍,并对其基本特性进行讲解说明。之后,我们将按步骤演示如何使用 Vivado 创建简单项目。手动实践部分将根据我们提供的 .v 和 .tb 代码,跟着步骤跑出 Simulation 结果即可。 Ⅰ. Verilog 基础…

Verilog HDL 基础语法

一、逻辑值

0: 逻辑低电平,条件为假

1: 逻辑高电平,条件为真

z: 高阻态,无驱动

x: 未知逻辑电平二、实际例子

1. 模块名一般与文件名相同 线网型变量会被映射成一条真实存在的物理连线。 寄存器型变量会被映射成一个寄存器。 2. 参数

para…

不可不知的FPGA内部结构